Контрольная работа: Мікросхеми з можливістю перепрограмування їх функцій

Схема керування і синхронізації містить дешифратор команд і керує роботою МП і виробляє сигнали керування для зовнішніх пристроїв (ОЗП, ПЗП, портів вводу-виводу).

Пристрій спряження з шиною, який інакше має назву шинний інтерфейс, містить блок сегментних регістрів, указник команд, суматор адрес, черга команд і буфери, що забезпечують зв’язок з шиною.

Шинний інтерфейс виконує операції обміну між МП і пам’яттю або портами вводу-виводу за запитаннями операційного пристрою.

Коли операційний пристрій зайнято виконанням команди, шинний інтерфейс самостійно ініціалізує вибірку кодів чергових команд з пам’яті.

Черга команд уявляє собою набір 8-розрядних регістрів і виконує роль регістра команд, в якому зберігаються коди, вибрані з програмної пам’яті.

Тривалість черги складається з 6 байт, що відповідає максимально тривалому формату команд.

Шинний інтерфейс ініціалізує вибірку наступного командного слова автоматично, як тільки в черзі звільняться два байти.

Як правило, в черзі знаходиться мінімум один байт потоку команд, так що операційний пристрій не очікує вибірки команди.

Зрозуміло, що випереджаюча вибірка команд дозволяє економити час тільки при звичайному порядку виконання команд.

В тих випадках, коли до моменту зчитування з’ясовується, що черга вільна, операційний пристрій очікує вибірку чергового командного слова, яку ініціалізує шинний інтерфейс.

Якщо команда потребує звертання до пам’яті або порту вводу-виводу, операційний пристрій запитує шинний інтерфейс на виконання необхідного циклу шини для передачі даних.

Сегментні регістри - CS, DS, ES і SS містять адреси сегментів коду, даних, додаткових даних і стека, відповідно.

Звичайно використовуються в таких парах: CS:IP, DS:SI, ES:DI,SS:SP.

Сегментація пам’яті і механізм формування фізичної адреси.

Фізична адреса МП ВМ86 містить 20 біт, таким чином його адресний простір містить 1МГб (![]() ). У цей же час сам процесор оперує логічними адресами, що містять 16 розрядів сегмента і 16 розрядів зміщення у сегменті. Тому необхідно перетворювати логічну 32-розрядну адресу у фізичну 20-розрядну.

). У цей же час сам процесор оперує логічними адресами, що містять 16 розрядів сегмента і 16 розрядів зміщення у сегменті. Тому необхідно перетворювати логічну 32-розрядну адресу у фізичну 20-розрядну.

Для цієї мети в суматорі адреси вміст сегментного регістра зсувається на 4 розряди і складається iз зміщенням у сегменті.

Можливі переноси в старші розряди (більші 20-го) при цьому втрачаються.

Таким чином, завдяки наявності сегментних регістрів весь простір пам’яті уявляється як набір сегментів. Сегментні регістри ініціалізуються на початку кожної програми шляхом завантаження в них відповідних констант.

Початкові адреси сегментів завжди кратні 16.

Інших обмежень на розміщення сегментів немає, тому вони мають можливість частково або повністю перекриватися. Якщо записати в усі сегментні регістри однакові константи, то отримаємо модель пам’яті, характерну для 8-розрядних МП (або SMALL для мови високого рівня - Паскаля чи Сі).

Дуплексна шина адреси-даних - за двоспрямованою шиною адреси-даних в режимі часового роозподілу можуть передаватися й адреси, й дані.

Така структура шини потребує, принаймнi, однієї додаткової зовнішньої мікросхеми, в якій можна було б фіксувати значення адреси і зберігати її, коли по шині почнеться передача даних.

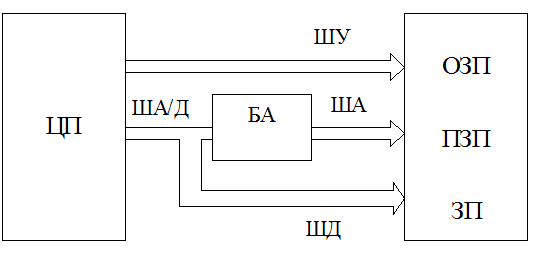

У мінімальному режимі структурну схему МП пристрою можна зобразити так, як це наведено на рис. 1.

Рисунок 1 - Структурна схема МП пристрою на МП 8086 у мінімальному режимі

До сигналів керування шиною відносяться сигнали:

MX/MN - вибір максимального (в багатопроцесорній системі) або мінімального режиму роботи МП;

M/IO - вибір пам’яті (=1) або зовнішніх пристроїв (=0), наприклад, при звертанні до ПЗП M/IO=1, цей сигнал тримається протягом всього машинного циклу;

ALE - строб адреси, на початку Т1 при ALE=1 на шині адреси-даних знаходиться адреса, цей сигнал скидається 0 на початку другого машинного такту;