Контрольная работа: Построение группового корректирующегоий кода объёмом 9 слов

![]()

![]()

![]()

![]()

(*)

Все колонки, кроме ![]() ,

, ![]() ,

, ![]() и

и ![]() , содержимое которых определяется формулами (*), заполняем цифрами из безызбыточного кода:

, содержимое которых определяется формулами (*), заполняем цифрами из безызбыточного кода:

| слово | безызбыточный код | код | |||||||

| 0001 | 0 | 0 | 0 | 1 | |||||

| 0010 | 0 | 0 | 1 | 0 | |||||

| 0011 | 0 | 0 | 1 | 1 | |||||

| 0100 | 0 | 1 | 0 | 0 | |||||

| 0101 | 0 | 1 | 0 | 1 | |||||

| 0110 | 0 | 1 | 1 | 0 | |||||

| 0111 | 0 | 1 | 1 | 1 | |||||

| 1000 | 1 | 0 | 0 | 0 | |||||

| 1001 | 1 | 0 | 0 | 1 | |||||

Чтобы заполнить колонки ![]() ,

, ![]() ,

, ![]() и

и ![]() , подставляем значения необходимых переменных в соответствующие уравнения из (*). Например, для строки 9 (слово

, подставляем значения необходимых переменных в соответствующие уравнения из (*). Например, для строки 9 (слово ![]() ) получаем следующее:

) получаем следующее:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

| слово | безызбыточный код | избыточный код | |||||||

| 0001 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | |

| 0010 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | |

| 0011 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | |

| 0100 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 0101 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 0110 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | |

| 0111 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | |

| 1000 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | |

| 1001 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | |

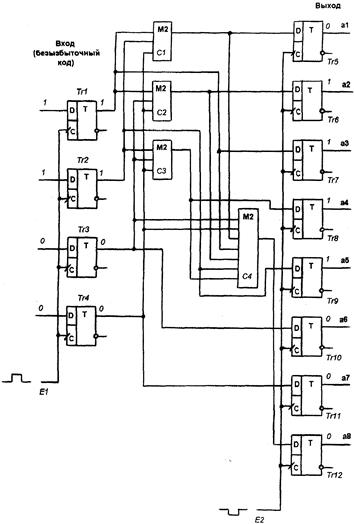

Перейдём к построению функциональной схемы кодирующего устройства (см. соответствующий рисунок ниже). Назначение кодирующего устройства – внесение избыточности в код по заданным нами правилам. Схему строим на основании равенств (*). На схеме используется логический элемент «сумматор по модулю два», обозначенный М2. На схеме имеются два регистра, построенные на D-триггерах. Один из них содержит безызбыточный код и имеет разрядность 4 бит, так как ![]() , а другой содержит избыточный код и имеет разрядность 8 бит, так как

, а другой содержит избыточный код и имеет разрядность 8 бит, так как ![]() . Принцип работы схемы таков: по сигналу синхронизации на k-разрядный регистр поступает кодовая комбинация, подлежащая кодированию. Затем с помощью сумматоров эта комбинация кодируется (вносится избыточность). Сумматор С1 реализует первое равенство из (*), сумматор С2 – второе, С3 – третье, а С4 – четвёртое. И, наконец, по сигналу синхронизации полученный избыточный код записывается в 8-разрядный регистр. Далее начинается кодирование следующей комбинации.

. Принцип работы схемы таков: по сигналу синхронизации на k-разрядный регистр поступает кодовая комбинация, подлежащая кодированию. Затем с помощью сумматоров эта комбинация кодируется (вносится избыточность). Сумматор С1 реализует первое равенство из (*), сумматор С2 – второе, С3 – третье, а С4 – четвёртое. И, наконец, по сигналу синхронизации полученный избыточный код записывается в 8-разрядный регистр. Далее начинается кодирование следующей комбинации.

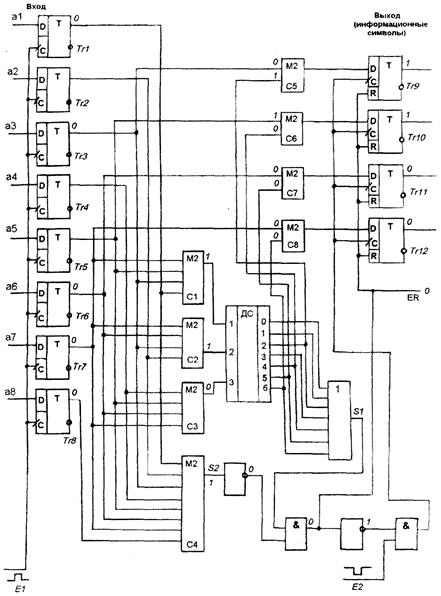

Далее рассмотрим функциональную схему декодирующего устройства (см. соответствующий рисунок ниже). В ней также используются два регистра на D-триггерах. Один из них содержит переданное слово и имеет разрядность 8 бит, так как ![]() , а другой содержит декодированные информационные символы и имеет разрядность 4 бит, так как

, а другой содержит декодированные информационные символы и имеет разрядность 4 бит, так как ![]() . Для построения схемы вспомним проверочные равенства, найденные ранее:

. Для построения схемы вспомним проверочные равенства, найденные ранее:

|

| (**) |

Обозначим буквой ![]() признак одиночной ошибки. Если

признак одиночной ошибки. Если ![]() , то имела место одиночная ошибка, если же

, то имела место одиночная ошибка, если же ![]() , то одиночной ошибки не было. Через

, то одиночной ошибки не было. Через ![]() обозначим результат общей проверки на чётность.

обозначим результат общей проверки на чётность.

![]()

Запишем алгоритм декодирования, пренебрегая возможностью возникновения ошибок кратности 3 и выше.

| Вывод | ||

| 0 | 0 | ошибок нет |

| 0 | 1 | ошибка в 8-ом разряде |

| 1 | 0 | двойная ошибка (повторная передача) |

| 1 | 1 | одиночная ошибка (исправление) |

Принцип работы дешифратора таков. На приёмный регистр поступает кодовая комбинация, которая может содержать ошибку. Сумматор С1 реализует первое равенство из (**), С2 – второе, а С3 – третье. Если ошибок не было, то на выходах этих трёх сумматоров будут нули. Если же имела место ошибка, то в этом случае на выходах сумматоров появится опознаватель ошибки. Этот опознаватель передаётся в дешифратор ошибок ДС, который на основании переданного в него опознавателя выдаёт соответствующий вектор ошибки. Его схема строится по следующей таблице истинности:

| Вход (опознаватель) | Выход (вектор ошибки) | ||||||||

| 1 | 2 | 3 | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Чтобы восстановить верный сигнал нам необходимо сложить по модулю два сигнал дешифратора с соответствующим разрядом кодовой комбинации. Эта операция выполняется на сумматорах С5-С8. Таким образом мы исправляем одиночные ошибки.

Чтобы обнаружить двойную ошибку, мы предусматриваем следующее. Сумматор С4 проверяет последнее равенство из (**) – на его выходе мы имеем ![]() . В случае возникновения двойной ошибки на выходе этого сумматора появится ноль, так как две единицы не изменят чётности (

. В случае возникновения двойной ошибки на выходе этого сумматора появится ноль, так как две единицы не изменят чётности (![]() ). Элемент ИЛИ проверяет признак одиночной ошибки (

). Элемент ИЛИ проверяет признак одиночной ошибки (![]() ). На этот элемент подаётся вектор ошибки с дешифратора. А если вектор ошибки содержит хотя бы одну единицу (а это значит, что имела место ошибка), то на выходе элемента ИЛИ появится единица. Таким образом, если на выходе С4 мы получили ноль, а на выходе элемента ИЛИ единицу, мы можем говорить, что имела место двойная ошибка. В этом случае блокируем генератор тактовых импульсов, триггеры устанавливаются в ноль, а на специально предусмотренный выход ER подаём единицу.

). На этот элемент подаётся вектор ошибки с дешифратора. А если вектор ошибки содержит хотя бы одну единицу (а это значит, что имела место ошибка), то на выходе элемента ИЛИ появится единица. Таким образом, если на выходе С4 мы получили ноль, а на выходе элемента ИЛИ единицу, мы можем говорить, что имела место двойная ошибка. В этом случае блокируем генератор тактовых импульсов, триггеры устанавливаются в ноль, а на специально предусмотренный выход ER подаём единицу.

Функциональная схема кодирующего устройства

Функциональная схема декодирующего устройства

Далее по функциональным схемам строим принципиальные электрические схемы. Для построения принципиальных схем используем программный пакет Multisim.