Курсовая работа: Разработка микропроцессорной системы

(2 кб)

Банк 3

(2 кб)

Банк 4

(2 кб)

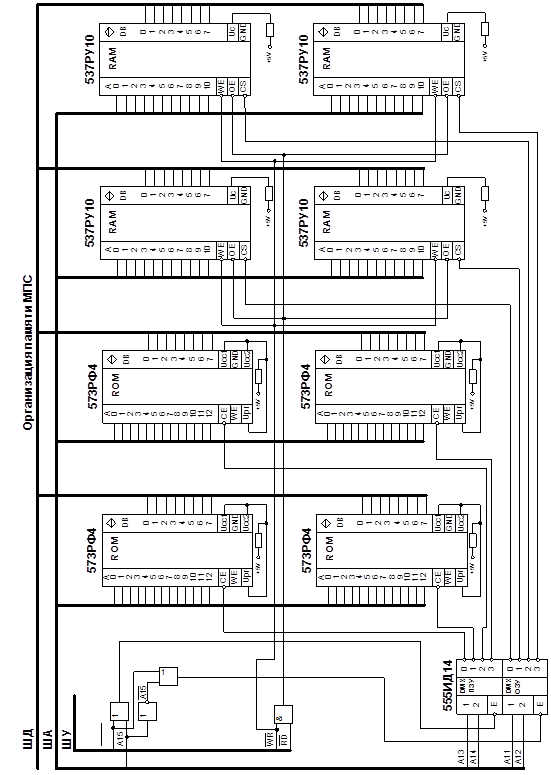

Из табл. 1 можно сделать следующие выводы по организации памяти:

· Шина данных подключается сразу ко всем восьми микросхемам.

· Для выбора той или иной микросхемы достаточно одного двойного демультиплексора 531ИД14, осуществляющего преобразование 1-4. Одна его часть отвечает за выбор схемы ПЗУ, другая – за выбор ОЗУ.

· Бит А15 равен 0, если адресуется ПЗУ и равен 1, когда адресуется ОЗУ.

· ПЗУ. По линии адреса на микросхему подаются биты А0‑А12, биты А13 и А14 определяют, в какой именно банк происходит адресация.

· ОЗУ. По линии адреса на микросхему подаются биты А0‑А10, биты А11 и А12 определяют конкретный банк, биты А13 и А14 всегда равны 0.

Сигналы с выхода демультиплексора подаются непосредственно на входы ![]() в ПЗУ и на входы

в ПЗУ и на входы ![]() в ОЗУ.

в ОЗУ.

Для активизации демультиплексора, отвечающего за ПЗУ, на вход ![]() необходимо подавать активный уровень сигнала (логический 0), если происходит цикл обращения к памяти (

необходимо подавать активный уровень сигнала (логический 0), если происходит цикл обращения к памяти (![]() ) и

) и ![]() . Необходимый управляющий сигнал достигается при использовании логического функции

. Необходимый управляющий сигнал достигается при использовании логического функции ![]() и элемента дисъюнктора. Справедливы аналогичные рассуждения для демультиплексора, отвечающего за ОЗУ, за исключением того факта, что в дисъюнкцию должно войти отрицание элемента

и элемента дисъюнктора. Справедливы аналогичные рассуждения для демультиплексора, отвечающего за ОЗУ, за исключением того факта, что в дисъюнкцию должно войти отрицание элемента ![]() –

– ![]() .

.

На вход ![]() ОЗУ необходимо подать логическую функцию

ОЗУ необходимо подать логическую функцию ![]() (логическое

(логическое ![]() , элемент конъюнктор), а на вход

, элемент конъюнктор), а на вход ![]() – выход МП

– выход МП ![]() .

.

Напряжения.

Т.к. ПЗУ не находится в режиме программирования, то на входы питания ПЗУ (![]() ,

,![]() ,

,![]() ) требуется подать +5V, а входы

) требуется подать +5V, а входы ![]() и

и ![]() – заземлить (на рис. не показано).

– заземлить (на рис. не показано).

На вход ОЗУ ![]() также подаётся +5V, а вход

также подаётся +5V, а вход ![]() заземляется.

заземляется.

Схема подключения памяти к шинам представлена на рис. 2.

Рисунок 2. Организация памяти

Организация ввода\вывода

По заданию МПС должна принимать и выдавать 16 ти битный код. Кроме того у МПС имеются перемычки для задания шестнадцатибитных констант регулятора ![]() ,

, ![]() ,

, ![]() .

.

На МПС должны быть 48 (16×3) перемычек для задания констант. Схема организации перемычек представлена на рис. слева. Перемычки собираются в группы по восемь (например, младший байт константы

На МПС должны быть 48 (16×3) перемычек для задания констант. Схема организации перемычек представлена на рис. слева. Перемычки собираются в группы по восемь (например, младший байт константы ![]() ) и подаются на приёмопередатчик 580ВА86. Таким образом задание трёх шестнадцатибитных констант требует шести 8‑ми битных приёмопередатчиков.

) и подаются на приёмопередатчик 580ВА86. Таким образом задание трёх шестнадцатибитных констант требует шести 8‑ми битных приёмопередатчиков.

Входной и выходной сигналы целесообразно хранить в регистрах, где они будут дожидаться запроса МП на чтение при вводе и запроса внешнего устройства (фронта синхросигнала) при выводе кода. Таким образом требуется наличие четырёх 8‑ми битных регистров.

Всего же требуется адресовать 10 устройств ввода\вывода. При этом задействуются биты А0‑А3. Запишем адреса внешних устройств в табл. 3.

Таблица 2. Адреса внешних устройств

| N | Внешний сигнал | Адрес |

| 1 | Входной сигнал | 0001:0000 |

| 2 | 0011:0010 | |

| 3 | 0101:0100 | |

| 4 | 0111:0110 | |

| 5 | Выходной сигнал | 1001:1000 |

Обращение к тому или иному внешнему сигналу в зависимости от его адреса осуществим с помощью демультиплексора 555ИД7 1-8 и дополнительных логических элементов. На вход демультиплексора подаются биты А0‑А2. Бит А3 отвечает за то, осуществляется ли адресация к портам ввода или вывода.

Рассмотрим случай адресации к младшему байту порта ввода данных или вывода. Обозначим ![]() – сигнал с выхода демультиплексора №0,

– сигнал с выхода демультиплексора №0, ![]() – сигнал, который подаётся на регистр, отвечающий за приём входного кода,

– сигнал, который подаётся на регистр, отвечающий за приём входного кода, ![]() – сигнал, отвечающий за запись в регистр выходного кода. Составим таблицу истинности (табл. 2). При этом необходимо помнить, что у

– сигнал, отвечающий за запись в регистр выходного кода. Составим таблицу истинности (табл. 2). При этом необходимо помнить, что у ![]() активный уровень

активный уровень ![]() (подключается к входу

(подключается к входу ![]() ), а

), а ![]() – сигнал положительной логики (подключается к входу

– сигнал положительной логики (подключается к входу ![]() ).

).

Таблица 3. Таблица истинности

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 |

Используя СКНФ, СДНФ и теорему де Моргана, запишем логические функции: