Курсовая работа: Шифратор фамилии на основе ДПСЧ

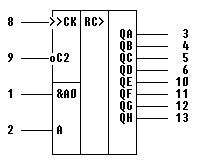

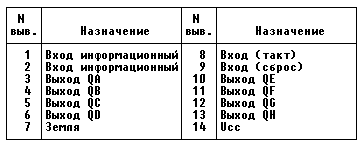

Рисунок 3 – изображение счетчика и назначение выводов

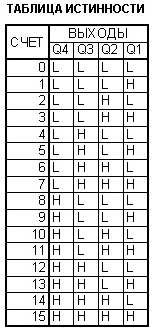

Рисунок 4 – Таблица истинности

Данная микросхема – четырехразрядный двоичный счетчик, выложенный на двухступенчатых триггерах J-K типа. Счетчик имеет два счетных входа С1, С2 и два входа установки нуля R01, R02. Вход 01 внутренне не соединён с последующими триггерами. Это даёт возможность использовать схему в двух независимых режимах работы в качестве: четырехразрядного двоичною счетчика, когда входные счетные импульсы поступают на вход С1. Выходы осуществляют операцию деления на два, четыре, восемь и шестнадцать; трехразрядною двоичного счетчика, когда входные счетные импульсы поступают на вход С2. Первый триггер, не соединенный с другими триггерами схемы, можно использовать как элемент для функции деления на два. Установочные входы микросхемы обеспечивают прекращение счета и возвращают все четыре триггера в состояние низкого уровня, когда на входы R01 и R02 одновременно подается высокий уровень напряжения. При операции счета на одном из входов установки R01 или R02 должен присутствовать потенциал низкого уровня. Таблица истинности показывает состояние на выходах схемы во время операции счета импульсов. (Выводы С2 и Q1 соединены, тактовые импульсы подаются на С1)

Регистр К555ИР9

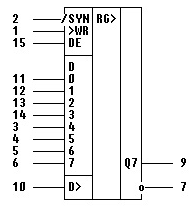

Рисунок 5 – Изображение регистра и назначение выводов

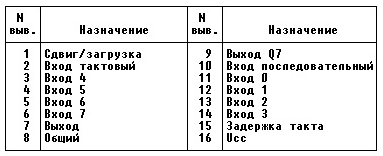

Рисунок 6 – Таблица истинности

Микросхема представляет собой восьмиразрядный сдвиговый регистр с параллельной загрузкой и имеет два режима работы: параллельная загрузка и сдвиг. Параллельная загрузка информации осуществляется при наличии на входе выбора «WR низкого уровня напряжения, причём загрузка происходит асинхронно.

После установки высокого уровня напряжения на входе выбора режима «WR по положительному фронту тактового импульса на входе синхросигнала SYN или входе блокировки синхросигнала DE происходит сдвиг. При высоком уровне напряжения на одном из входов SYN или DE состояние регистра не изменяется.

Регистр К555ИР8

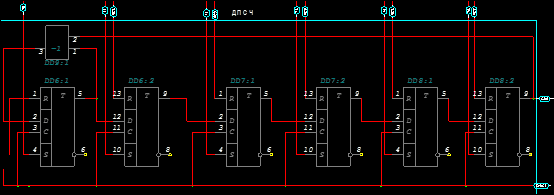

Рисунок 7 – Изображение регистра и назначение выводов

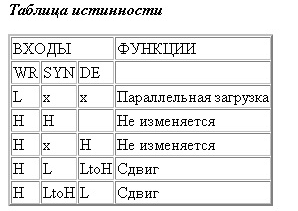

Рисунок 10 – Таблица истинности

Микросхема представляет собой восьмиразрядный сдвиговый регистр с последовательной загрузкой и параллельной выгрузкой. Наличие двух входов загрузки А и &А позволяет использовать один из них в качестве управляющего загрузкой данных: низкий уровень на одном из них запрещает прохождение сигнала со второго.

Низкий уровень на входе R устанавливает все выходы микросхемы в 0.

Описание работы схемы шифратора

Кнопки управления

S1:1 – кнопка занесения информации в блок хранения и обработки информации

S8:1 – кнопка начала кодирования

S3:1, S4:1, S5:1, S6:1, S7:1, S9:1 – кнопки установки начального состояния ДПСЧ

Датчик псевдослучайных чисел (ДПСЧ)

Цель ДПСЧ генерация гамма кода, который необходим для шифрования информации путем сложения каждого бита сообщения с последовательностью битов ДПСЧ по модулю.

Счетчик тактов