Лабораторная работа: Разработка кодирующего устройства для формирования сверточного кода

Сверточный код можно рассматривать как обобщение блочного кода, понимая при этом под значением ![]() – длину информационного сообщения и этой длине информационного сообщения будет соответствовать суммарная длина кодовой комбинации, которая отправляется в канал передачи данных -

– длину информационного сообщения и этой длине информационного сообщения будет соответствовать суммарная длина кодовой комбинации, которая отправляется в канал передачи данных - ![]() , (

, ( ![]() ).

).

1. Разработка структурной схемы системы передачи данных (СПИ), ее описание

В систему передачи информации входят следующие элементы (рис.1).

Рисунок 1

Кодирующее устройство (кодер) решает задачу введения некоторой избыточности в виде дополнительных символов, передаваемого сообщения статистического кода. Эта избыточность нужна для наделения кода свойством исправлять ошибки. Может использоваться любое представление корректирующего кода, либо двоичное, либо недвоичное (в нашем примере двоичное представление).

Модулятор осуществляет кодирование сигнала по определенному способу модуляции сигнала – амплитудное, частотное, фазовое телеграфирование (в нашем примере фазовое телеграфирование). Для каждого сигнала существуют свои зависимости. При постоянной величине отношения энергии сигнала к энергии шума (помех) вероятность ошибки в приеме бита информации наиболее низкая при использовании фазового телеграфирования.

Демодулятор осуществляет декодирование сигнала, тип которого определяется способом модуляции сигнала. Декодер выполняет функции: 1) обнаружение ошибок; 2) исправление обнаруженных ошибок; 3) дешифрование принятого статистического кода (выделение статистического кода). Возможно, декодер не выполнит своих функций и произойдет трансформация статистического кода в другое разрешенное сообщение, что является крайне опасным явлением. Различают последовательное декодирование сверточных кодов (применим для систематических кодов, особенно для (2,1), обладает пороговыми свойствами), а также декодирование по методу максимального правдоподобия, то есть оптимальным образом. Оптимальное декодирование предполагает, что декодер будет исправлять большее число ошибок, чем пороговое значение.

2. Разработка кодирующего устройства для формирования сверточного кода

2.1 Разработка структурной схемы кодирующего устройства для формирования сверточного кода

Основой для построения структурной схемы кодирующего устройства для формирования сверточного кода является:

1) заданное число разрядов регистра сдвига, k=5;

2)

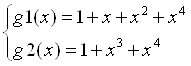

система образующих полиномов:

3) скорость формирования сверочного кода,

,

,

где ![]() - число символов сообщения, которые поступают на вход кодирующего устройства для формирования определенного отрезка кодовой комбинации

- число символов сообщения, которые поступают на вход кодирующего устройства для формирования определенного отрезка кодовой комбинации ![]() .

.

Число разрядов регистра либо задано, либо его определяют по старшей степени в системе образующих полиномов, степень X (в данном случае 4+1=5=k) будет образовать число разрядов. Сумматоров по mod2 ставится столько, сколько образующих полиномов в нашей системе. Связи сумматоров с триггерами регистра сдвига определяются соответствующими коэффициентами многочленов.

Рисунок 2 Структурная схема кодирующего устройства

Коммутатор "опрашивает" выходы сумматоров по mod2 по приходу каждого информационного символа и выдает последовательно символы в канал передачи данных, то есть по приходу одного символа сообщения в канал передачи данных поступает два символа кодовой последовательности.

2.2 Разработка функциональной электрической схемы кодирующего устройства для формирования сверточного кода

На основе структурной схемы кодера построим функциональную электрическую схему кодирующего устройства (рис.3). При аппаратной реализации используем конструкции на интегральных цифровых микросхемах. Среди серий ИМС выбираем К555 (ТТЛШ – транзисторно-тразисторная логика с использованием диодов Шотки).

Микросхема К555ИР8 - 8-разрядный регистр с последовательной загрузкой и параллельной выгрузкой. Входы: 2 - информационный вход, 8 - тактовый вход, 9 - сброс. Выходы: 3, 4, 5, 6, 10, 11, 12, 13.

Микросхема К555ИР9 - 8-разрядный сдвиговый регистр с параллельной загрузкой и имеет два режима работы: параллельная загрузка и сдвиг. Входы: WR – вход выбора режима; SYN – тактовый вход; входы параллельной загрузки – 3, 4, 5, 6, 11, 12, 13, 14. Выход: 9 – Q7.

Микросхема К555ЛП5 – четыре двухвходовых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (сумматор по mod2).

Микросхема К555ТВ15 – два JK-триггера. Используется в качестве счетного Т-триггера, выполняющего функцию деления частоты на 2. Входы: 4, 12 – входы синхронизации; 1, 15 – входы установки нуля; 5, 11 – входы установки единицы; Выходы: 6, 10 – прямые выходы.

Микросхема К555ЛИ1 – 4 элемента 2И.