Реферат: Разработка вычислительного устройства

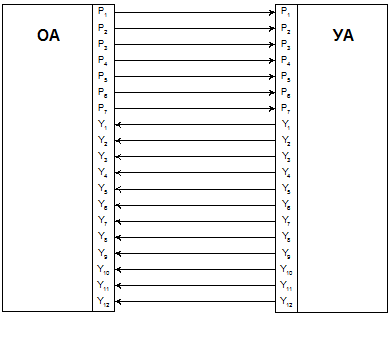

Рисунок 4

Числовые тестовые примеры выполнения операций с пояснениями

Пусть X=11010111*23 , Y=1101*22 . Найти частное от деления X/Y.

Все действия выполняются в устройстве в следующей последовательности:

| 0.1101111 | Прямой код делимого | Частное X/Y |

| + | 1.0011 | Дополнительный код делителя |

| 0.0000 | Остаток положительный | 1 |

| 0.0000 | Остаток сдвинут влево на один разряд | |

| + | 1.0011 | Дополнительный код делителя |

| 1.0011 | Остаток отрицательный | 10 |

| 0.0111 | Остаток сдвинут влево на один разряд | |

| + | 0.1101 | Прямой код делителя |

| 1.0100 | Остаток отрицательный | 100 |

| 0.1001 | Остаток сдвинут влево на один разряд | |

| + | 0.1101 | Прямой код делителя |

| 1.0110 | Остаток отрицательный | 1000 |

| 0.1101 | Остаток сдвинут влево на один разряд | |

| + | 0.1101 | Прямой код делителя |

| 1.1010 | Остаток отрицательный | 10000 |

Одновременно вычисляется порядок частного следующим образом:

pc = px - py = 0.011 - 0.010 = 0.001

Описание функциональной схемы устройства.

Функциональная схема устройства представлена на рисунке 5.

Функциональная схема реализует схему работы с мантиссами.

Используемый мультиплексор 2´1 на вход которого подается число в прямом и дополнительном коде и в зависимости от ситуации выбирается одно из двух чисел. В процессе работы осуществляется контроль делителя на равенство нулю, поэтому используемый мультиплексор должен иметь стробируемый вход.

Сумматор складывает числа, которые пришли с выхода мультиплексора и регистра Am , результат переписывается в регистр Am , который запоминает это число, сдвигает его влево в сторону старших разрядов и снова передает его на сумматор.

Так же старший разряд регистра подается на результирующий последовательно параллельный регистр Z, в котором происходит накопление результата. После определение результата, полученное число надо нормализовать и поэтому результирующий регистр кроме последовательного входа и параллельного вывода должен осуществлять сдвиг числа влево в сторону старших разрядов.

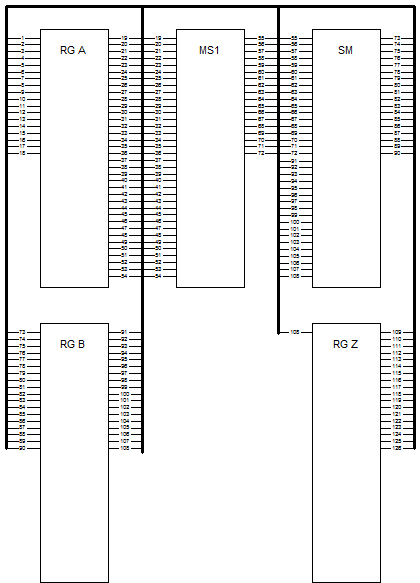

Рисунок 5

Краткое описание принципиальной схемы

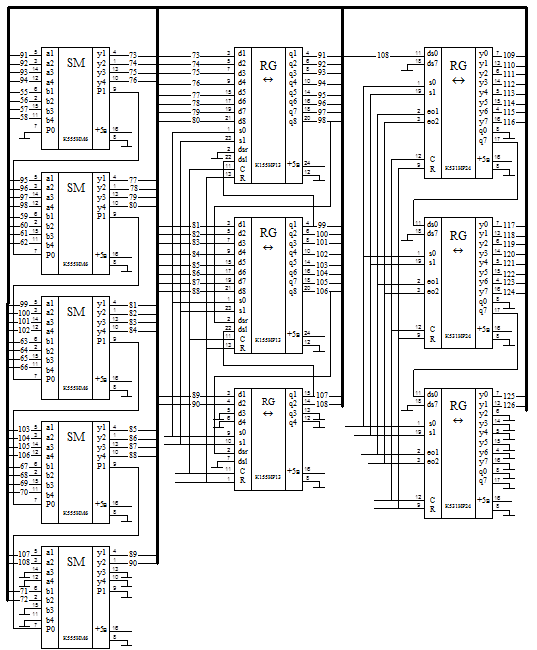

Принципиальная схема устройства представлена на рисунке 6.

Два числа поступают на сумматор, который их суммирует и передает результат на регистр. В качестве сумматора используется микросхема К555ИМ6, а в качестве регистра К155ИР13 и К555ИР11 которые отличаются только разрядностью. Старший разряд регистра поступает на вход результирующего последовательно – параллельного регистра, в котором накапливается результат. В данной схеме в качестве результирующего регистра используется микросхема К531ИР24.

Рисунок 6

Заключение

В данной курсовой работе было разработано вычислительное устройство, выполняющее следующие операции:

· Нахождение абсолютного значения числа.

· Деление чисел в формате с плавающей запятой.

Построен алгоритм обработки чисел. Расписаны управляющие сигналы и префиксные функции. По имеющемся данным построена функциональная схема устройства. Также была построена принципиальная схема указанной части устройства, в которой были использованы конкретные микросхемы.Приведен тестовый пример выполнения операций.