Реферат: Шифраторы, дешифраторы, триггеры

В этой схеме, если на информационный вход триггера подавать сигнал![]() и поменять местами выходы, получится D -триггер, информационный вход которого работает по негативной логике.

и поменять местами выходы, получится D -триггер, информационный вход которого работает по негативной логике.

Рассмотрим триггеры со счётными входами, или так называемые Т -триггеры. В простейшем случае Т -триггер можно построить на двух RS -триггерах типа рисунка 2-2а, с добавлением некоторых входов или вентилей, как это делается обычно при построении Т -триггера на булевых элементах. Однако при этом потребуются 4-6 элементов, то есть схема получается сложной.

На рисунке 2-4 показана схема счётного триггера, построенная на трёх мажоритарных элементах. Для работы в счётном режиме на управляющие входы y1 и y2 подаётся постоянно высокий уровень потенциала 1. При каждом поступлении счётного сигнала Т выход Q -триггера переключается в противоположное состояние, причём рабочим перепадом является отрицательный перепад счётного сигнала, то есть триггер работает по принципу Master-Slave, МЭ1 и МЭ2 образуют ведущий триггер, а МЭ3 -ведомый. На рисунке 2-4 справа показана временная диаграмма работы триггера. Максимальная частота переключения этого триггера в счётном режиме равна: ![]() , где τ-задержка одного элемента.

, где τ-задержка одного элемента.

![]()

На рисунке 2-5 приведены схемы Т - и RST -триггеров, построенных на двух ФНР и ФНО соответственно. Обе схемы работают согласно временной диаграмме, приведённой на рисунке 2-5 внизу. Верхний нейрон Нм реагирует на положительный перепад счётного сигнала и называется ведущим (Master) элементом, а нижний нейрон Н s реагирует на отрицательный перепад счётного сигнала и называется ведомым (Slave) элементом. Ведомый нейрон Н s напоминает предыдущее состояние триггера на время, равное длительности запускающего сигнала. Это свойство схемы в некоторый момент времени содержать в себе информацию как о текущем, так и о предыдущем состоянии – очень важно. Как будет показано далее, оно широко используется при построении логических устройств на таких триггерах.

На рисунке 2-5 приведены схемы Т - и RST -триггеров, построенных на двух ФНР и ФНО соответственно. Обе схемы работают согласно временной диаграмме, приведённой на рисунке 2-5 внизу. Верхний нейрон Нм реагирует на положительный перепад счётного сигнала и называется ведущим (Master) элементом, а нижний нейрон Н s реагирует на отрицательный перепад счётного сигнала и называется ведомым (Slave) элементом. Ведомый нейрон Н s напоминает предыдущее состояние триггера на время, равное длительности запускающего сигнала. Это свойство схемы в некоторый момент времени содержать в себе информацию как о текущем, так и о предыдущем состоянии – очень важно. Как будет показано далее, оно широко используется при построении логических устройств на таких триггерах.

Рассмотрим работу триггера рисунка 2-5а. Допустим, что триггер находится в состоянии 0, то есть Q’= Q=0 , и на вход Т поступает сигнал (высокий потенциал). Этот сигнал возбуждает нейрон Нм через синапс с весом +1, а нейрон Н s остаётся в невозбуждённом состоянии, поскольку в нём до переключения Нм возбуждены два синапса с весами +1 и –2 и суммарная активность![]() , а после переключения Нм возбуждены все три синапса с весами +1 и –2 и суммарная активность

, а после переключения Нм возбуждены все три синапса с весами +1 и –2 и суммарная активность![]() . Таким образом, пока на входе Т стоит высокий потенциал, Нм находится в возбуждённом состоянии, а Н s – в невозбуждённом. После снятия сигнала на входе Т (подан низкий потенциал) нейрон Н s также переходит в возбуждённое состояние благодаря синапсу, связанному с выходом Q’, а нейрон Нм не изменяет своего состояния. Следовательно, за один период входного сигнала триггер переключается полностью из состояния 0 в состояние 1. Обратное переключение из состояния 1 в состояние 0 происходит аналогичным образом.

. Таким образом, пока на входе Т стоит высокий потенциал, Нм находится в возбуждённом состоянии, а Н s – в невозбуждённом. После снятия сигнала на входе Т (подан низкий потенциал) нейрон Н s также переходит в возбуждённое состояние благодаря синапсу, связанному с выходом Q’, а нейрон Нм не изменяет своего состояния. Следовательно, за один период входного сигнала триггер переключается полностью из состояния 0 в состояние 1. Обратное переключение из состояния 1 в состояние 0 происходит аналогичным образом.

Максимальное быстродействие триггера на рисунке 2-5 в счётном режиме равно: ![]() . Для установки триггера в состояние 0 или 1 достаточно на соответствующий вход подать положительный импульс с длительностью

. Для установки триггера в состояние 0 или 1 достаточно на соответствующий вход подать положительный импульс с длительностью ![]() , то есть R- и S- входы триггера работают по асинхронному принципу.

, то есть R- и S- входы триггера работают по асинхронному принципу.

![]()

На рисунке 2-6 показан ведущий-ведомый (Master-Slave) D- триггер (далее будем называть MSD- триггером) с пара фазным входом и временная диаграмма его работы. При поступлении синхроимпульса его положительный перепад записывает информацию D в ведущем нейроне Нм , при этом состояние ведомого нейрона остаётся прежним. Отрицательный перепад синхроимпульса, состояние ведущего нейрона записывает в ведомом нейроне Н s . Как видно, информация на выходе этого триггера появляется с задержкой, равной длительности синхроимпульса. Поэтому этот триггер иногда называют также задержанным D- триггером в отличие от простого D- триггера.

На рисунке 2-6 показан ведущий-ведомый (Master-Slave) D- триггер (далее будем называть MSD- триггером) с пара фазным входом и временная диаграмма его работы. При поступлении синхроимпульса его положительный перепад записывает информацию D в ведущем нейроне Нм , при этом состояние ведомого нейрона остаётся прежним. Отрицательный перепад синхроимпульса, состояние ведущего нейрона записывает в ведомом нейроне Н s . Как видно, информация на выходе этого триггера появляется с задержкой, равной длительности синхроимпульса. Поэтому этот триггер иногда называют также задержанным D- триггером в отличие от простого D- триггера.

Как известно, универсальным типом триггера является JK- триггер, который может работать как в режиме синхронного RS- триггера, так и в режиме Т- триггера и MSD- триггера. Рассмотренный на рисунке 2-4 Т- триггер можно превратить в JK- триггер, если на управляющие входы y1 и y2 подать сигналы J и K соответственно, а на вход Т подать синхроимпульсы. Если же на вход у1 подать сигнал D , а на вход y2 - сигнал![]() , то этот триггер превратится в MSD- триггер с парафазным входом.

, то этот триггер превратится в MSD- триггер с парафазным входом.

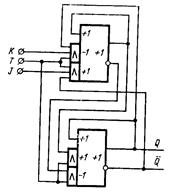

На рисунке 2-7 приведена схема JK- триггера на ИЛИ – нейронах. Хотя в схеме используются прямое и инверсное значения тактирующего сигнала, но соревнование (гонка) сигналов полностью отсутствует. При J= K=1 тактирующий сигнал не влияет на триггер. Если J= K=0 или эти входы объединены с входом

На рисунке 2-7 приведена схема JK- триггера на ИЛИ – нейронах. Хотя в схеме используются прямое и инверсное значения тактирующего сигнала, но соревнование (гонка) сигналов полностью отсутствует. При J= K=1 тактирующий сигнал не влияет на триггер. Если J= K=0 или эти входы объединены с входом ![]() , то триггер работает в счётном режиме, то есть превращается в Т- триггер. В остальных случаях тактирующий сигнал записывает входную информацию в триггер, причём снова верхний нейрон является ведущим, а нижний - ведомым.

, то триггер работает в счётном режиме, то есть превращается в Т- триггер. В остальных случаях тактирующий сигнал записывает входную информацию в триггер, причём снова верхний нейрон является ведущим, а нижний - ведомым.

![]() Рассмотрим работу приведённого JK- триггера. В исходном состоянии отсутствует тактирующий сигнал, то есть C=0 , а

Рассмотрим работу приведённого JK- триггера. В исходном состоянии отсутствует тактирующий сигнал, то есть C=0 , а ![]() . При этом триггер может находиться либо в состоянии 0, либо в 1. Оба эти состояния триггера устойчивые. Действительно, допустим триггер находится в состоянии 0. Это означает, что Q= Q’=0 . Нм не возбуждён, так как в нём возбуждены один положительный и один отрицательный входы, сумма весов которых меньше порога (+1). Следовательно, состояние Нм устойчивое. В Н s возбуждён отрицательный вход, связанный с

. При этом триггер может находиться либо в состоянии 0, либо в 1. Оба эти состояния триггера устойчивые. Действительно, допустим триггер находится в состоянии 0. Это означает, что Q= Q’=0 . Нм не возбуждён, так как в нём возбуждены один положительный и один отрицательный входы, сумма весов которых меньше порога (+1). Следовательно, состояние Нм устойчивое. В Н s возбуждён отрицательный вход, связанный с ![]() . Поэтому состояние Н s также устойчивое.

. Поэтому состояние Н s также устойчивое.

Аналогичным образом устойчиво также единичное состояние триггера, когда Q= Q’=1 , благодаря обратным связям с прямых выходов нейронов к своим же положительным входам.

При отсутствии тактирующего сигнала (С=0 ) изменение информации на входах J и K не влияет на триггер. Допустим триггер находится в состоянии 0 и J=1 , K=0 . Пока С=0 , то есть ![]() , сигнала J не действует на положительный вход Нм , связанный с элементом ИЛИ, остаётся возбуждённым, так как J=1 , а тормозящий вход гасится, так как К=0 . В результате Нм возбуждается, то есть Q’=1 . Этот сигнал не может возбуждать Н s пока С=1 . При снятии тактирующего сигнала высокий потенциал выхода Q’ поддерживает Нм в возбуждённом состоянии и одновременно возбуждает Н s , то есть получается Q=1 .

, сигнала J не действует на положительный вход Нм , связанный с элементом ИЛИ, остаётся возбуждённым, так как J=1 , а тормозящий вход гасится, так как К=0 . В результате Нм возбуждается, то есть Q’=1 . Этот сигнал не может возбуждать Н s пока С=1 . При снятии тактирующего сигнала высокий потенциал выхода Q’ поддерживает Нм в возбуждённом состоянии и одновременно возбуждает Н s , то есть получается Q=1 .

Таким образом, положительный перепад тактирующего сигнала переключает Нм , а отрицательный перепад – Hs . В итоге после одного тактирующего импульса триггер переключается из состояния 0 в состояние 1.

![]()

В этом состоянии, когда Q=1, J=1, K=0 , при повторном поступлении тактирующего сигнала состояние Нм , следовательно, и состояние всего триггера не изменится, так как при С=1 ,

В этом состоянии, когда Q=1, J=1, K=0 , при повторном поступлении тактирующего сигнала состояние Нм , следовательно, и состояние всего триггера не изменится, так как при С=1 , ![]() оба входа Нм остаются возбуждёнными, причём положительный вход от сигнала J , отрицательный вход от сигнала Q .

оба входа Нм остаются возбуждёнными, причём положительный вход от сигнала J , отрицательный вход от сигнала Q .

При соединении входов J и K с входом ![]() или при подаче на входы J и K постоянного низкого потенциала (J= K=0 ) триггер изменяет своё состояние на противоположное при каждом поступлении тактирующего сигнала С , то есть превратиться в Т- триггер.

или при подаче на входы J и K постоянного низкого потенциала (J= K=0 ) триггер изменяет своё состояние на противоположное при каждом поступлении тактирующего сигнала С , то есть превратиться в Т- триггер.

Работу описанного JK- триггера можно выразить следующим образом:

![]()

, где Q( t) – состояние триггера в момент t .

Если на входы J и K триггера подавать инверсные значения сигналов, то триггер будет работать аналогичным образом. Для перехода в счётный режим необходимо на эти входы подавать сигнал 1 или объединить их со сходом С .

На рисунке 2-8 показан вариант JK -триггера, где используются однополярные тактирующие сигналы C и все выходы работают по позитивной логике.

Можно привести множество других вариантов триггеров, построенных на ПЭ и ФН различных типов.

ИСПОЛЬЗОВАННАЯ ЛИТЕРАТУРА

- С.О.Мкртчян «Проектирование логических устройств ЭВМ на нейронных элементах», Москва, «Энергия», 1977, Стр.74-78

- С.О.Мкртчян «Проектирование логических устройств ЭВМ на нейронных элементах», Москва, «Энергия», 1977, Стр.40-49