Учебное пособие: Интегральные микросхемы

I этап (1969 - 1975 гг.). В состав стандартных серий входили микросхемы малой степени интеграции, выполняющие простейшие логические функции, например серия К155.

II этап (1976 - 1980 гг.). Появились серии с улучшенными характеристиками, такие как 531, 555, 500, К561, К1561 и другие, что привело к ограниченному применению серий 131, 158, 137, 187.

III этап (1981 - 1987 гг.). Разработка микросхем большой степени интеграции, микропроцессорных комплектов, запоминающих устройств, полузаказных БИС на основе матричных кристаллов.

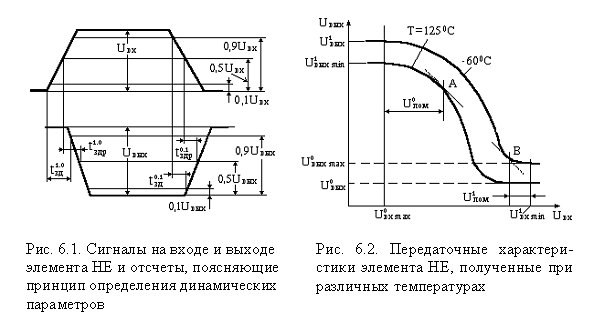

Параметры микросхем конкретной серии в основном определяются параметрами базовых элементов логики. К основным параметрам относятся: быстродействие; потребляемая мощность (Рпот ); помехоустойчивость Uпом ; коэффициент разветвления по выходу (нагрузочная способность) Краз ; коэффициент объединения по входу Коб . Быстродействие определяется динамическими параметрами цифровых микросхем, к которым относятся: t1,0 - время перехода сигнала на выходе микросхемы из состояния логической “1” в состояние логического “0”; t0,1 -время перехода из состояния низкого уровня в состояние высокого уровня; t1,0 здр - время задержки распространения при включении; t1,0 зд -время задержки включения; t0,1 здр - время задержки распространения при выключении; t0,1 зд - время задержки выключения; tздрср - среднее время задержки распространения сигнала; fр - рабочая частота. Среднее время задержки распространения tэдрср = 0,5(t1,0 здр + t0,1 здр ) является усредненным параметром быстродействия микросхемы, используемым при расчете временных характеристик последовательно включенных цифровых микросхем. На рис. 6.1 показаны уровни отсчета, определяющие параметры быстродействия цифровых микросхем.

В зависимости от технологии микросхем, мощности, потребляемые при состоянии логического нуля и при состоянии логической “1” могут отличаться. Поэтому, мощность, потребляемая логическими элементами в динамическом режиме, определяется как

Рпотср = 0,5(Р0 пот + Р1 пот ),

где Р0 пот - мощность, потребляемая микросхемой при состоянии выхода “0”, Р1 пот - мощность при выходном состоянии “1”.

Некоторые логические элементы кроме статической средней мощности характеризуются мощностью, потребляемой на максимальной частоте переключения, когда токи в цепях питания возрастают во много раз. К таким схемам относятся микросхемы КМОП технологии, которые потребляют микроамперы, если нет переключающих сигналов.

Допустимый уровень напряжения помехи логического элемента определяется уровнем входного напряжения, при котором еще не происходит ложное срабатывание микросхемы.

В статическом режиме помехоустойчивость определяется по низкому U0 пом и высокому U1 пом уровням. Значения U0 пом и U1 пом определяют с помощью передаточных характеристик (рис. 6.2.). Как следует из рис. 6.2, напряжение помехи по высокому уровню определяется как разность минимального напряжения высокого уровня U1 вхmin и напряжения в точке перегиба верхней кривой (точка В). Параметр U0 пом определяется как разность напряжения низкого уровня U0 вхmax .

Помехоустойчивость в динамическом режиме зависит от длительности, амплитуды и формы импульса помехи, а также от запаса статической помехоустойчивости и скорости переключения логического элемента.

Коэффициент разветвления по выходу Краз определяет число входов аналогичных элементов, которое может быть подключено к выходу предыдущего элемента без нарушения его работоспособности. С увеличением нагрузочной способности расширяются возможности применения цифровых микросхем и уменьшается число корпусов в разрабатываемом устройстве. Однако при этом ухудшаются помехоустойчивость и быстродействие микросхемы и возрастает потребляемая мощность.

Коэффициент объединения по входу Коб определяет максимальное число входов цифровых микросхем.

Базовые логические элементы

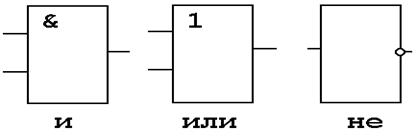

Существуют три базовых логических элемента, выполняющих логические операции сложения, умножения и отрицания: элемент И, элемент ИЛИ и элемент НЕ (инвертор), которые обозначаются на принципиальных электрических схемах как показано на рис.1

Рис. 1. Базовые логические элементы.

Работа логического элемента может быть представлена таблицей истинности, в которой указаны состояния входов (A,B и т.д.) и выходов (F):

Элемент И F=A.B Элемент ИЛИ F=A+B Элемент НЕ F=A

| Вх A | Вх B | Выход F | Вх A | Вх B | Выход F | Вход | Выход |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | 1 | 1 |

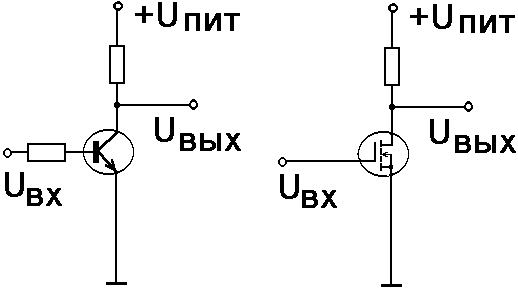

Знак отрицания (инверсии) обычно обозначается чертой над буквой ![]() , а на принципиальной схеме - кружком у соответствующего вывода. Практическая реализация инвертора на биполярном и МОП транзисторах показана на рис.2. Количество входов у логического элемента может быть больше двух, в этом случае тоже можно легко построить таблицу истинности. В практических схемах иногда существуют незадействованные входы, которые нужно соединить, в соответствии с логикой схемы, с общим проводом (землей) или через резистор с проводом питания (для ТТЛ-схем Uпит=+5В).

, а на принципиальной схеме - кружком у соответствующего вывода. Практическая реализация инвертора на биполярном и МОП транзисторах показана на рис.2. Количество входов у логического элемента может быть больше двух, в этом случае тоже можно легко построить таблицу истинности. В практических схемах иногда существуют незадействованные входы, которые нужно соединить, в соответствии с логикой схемы, с общим проводом (землей) или через резистор с проводом питания (для ТТЛ-схем Uпит=+5В).

Рис. 2. Инвертор на основе биполярного и МОП транзисторов

Комбинируя базовые логические элементы, можно получить достаточно сложную схему. Для схемы ИЛИ различают обычное ИЛИ (включающее) и исключающее ИЛИ.

| Исключающее ИЛИ | Элемент ИЛИ-НЕ | ||||

| Вх A | Вх B | Выход F | Вх A | Вх B | Выход F |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 |

Триггеры

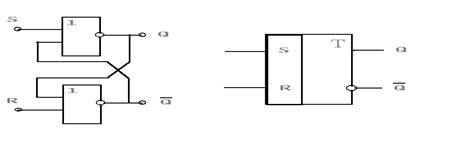

Триггер - электронное устройство, которое может находиться в двух устойчивых состояниях, поэтому они применяются в статических оперативных запоминающих устройствах (СОЗУ) как элемент памяти на один бит информации. Триггеры подразделяются на тактируемые (синхронные) и нетактируемые (асинхронные). Синхронный триггер меняет свое только при подаче определенного сигнала на тактируемый вход, причем тактирование может, осуществляется как по уровню ("1" или "0"), так и по фронту сигнала (переход "1" -> "0" или наоборот). Различают RS, D, T и JK триггеры. На рис.3 показана реализация асинхронного RS-триггера на ИЛИ-НЕ элементах (подумайте: как реализовать RS-триггер на И-НЕ элементах). Входы триггера обозначены буквами R (reset-сброс) и S (set-установка). Таблица истинности RS-триггера на элементах ИЛИ-НЕ приведена ниже.

| S | R | Q | Qinv |

| 0 | 0 | 0 | Qinv |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | x | x |

Здесь состояние S=1 и R=1 является неопределенным (проанализируйте работу схемы и скажите почему?).

Рис.3 RS-триггер

D-триггер (delay-задержка) имеет два входа: D - информационный и C - тактовый (рис,4 А) и работает с нижеприведенной таблицей),тактирование осуществляется передним фронтом):

| C | D | Q | Qinv |

|

0->1 К-во Просмотров: 688

Бесплатно скачать Учебное пособие: Интегральные микросхемы

|