Учебное пособие: Програмування універсальних мікропроцесорів на мовах Асемблер

- Масштаб (Scale) - множник (1, 2, 4 або 8), зазначений у коді інструкції. Цей елемент використовується для вказівки розміру елемента масиву, доступний тільки при 32-бітній адресації.

Окремі доданки в цій формулі можуть бути відсутніми.

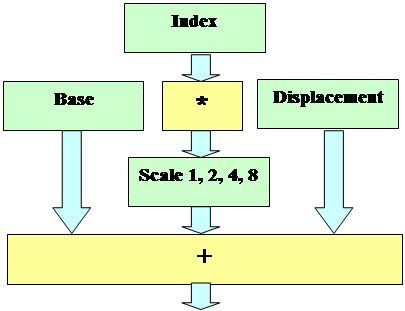

Обчислення ефективної адреси пояснюється схемою, представленої на рис. 1. Можливі режими адресації представлені в таблиці 1.

Процесори ІA-32 можуть працювати з 32-бітною або 16-бітною адресацією. 16-бітна адресація функціонує так само, як у МП І8086 , при цьому як компоненти адреси використовуються молодші 16 біт відповідних регістрів. Як говорилося вище, у реальному режимі за замовчуванням використовується 16-бітна адресація, однак є можливість для поточної інструкції переключитися на 32-бітну. При 32-бітній адресації застосовуються розширені 32-розрядні регістри і додаткові режими з масштабуванням індексу. Однак значення ефективної адреси, що обчислюється, усе рівно не може вийти за 64-килобайтний бар'єр - при спробі використання ЕА , що виходить за межу сегмента генерується виключення #GP (General Protectіon Fault).

ЕА

Рис. 1. Обчислення ефективної адреси

Таблиця 1

| Режим | Адреса |

| Пряма адресація | EA = Disp |

| Непряма регістрова адресація | EA = Base |

| Базова адресація | EA = Base +Disp |

| Індексна адресація | EA = Index +Disp |

| Масштабована індексна адресація | EA = Index* Scale +Disp (*) |

| Базово-індексна адресація | EA = Base +Index |

| Масштабована базово-індексна адресація | EA = Base +Index* Scale (*) |

| Базово-індексна адресація зі зсувом | EA = Base +Index +Disp (*) |

| Масштабована базово-індексная адресація зі зсувом | EA = Base +Index* Scale +Disp |

(*)- масштабування індексу можливо тільки при 32-бітній адресації.

Нагадаємо, у цій ситуації при 16-бітній адресації просто ігнорується перенос у розряд А16 і сегмент "звертається в кільце".

Засоби контролю стежать і за переходом через границю сегмента під час звертання до "прикордонної" адресі. При спробі адресації до слова, що має зсув FFFF16 або до подвійного слову зі зсувом FFFD16 - FFFF16 (їх старші байти виходять за межу сегмента), або виконання інструкції, хоча б один байт якої не уміщається в даному сегменті, процесор також виробляє виключення #GP.

У захищеному режимі також можливе переключення 16-и і 32-бітної адресації.

Розходження між режимами адресації при використанні 16-и і 32-бітної адресації показані в таблиці 2.

Таблиця 2.

| Компонент | 16-бітна адресація | 32-бітна адресація |

| Базовий регістр | ВХ або ВР | Будь-який 32-бітний регістр загального призначення. |

| Індексний регістр | SI або DI | Будь-який 32-бітний регістр загального призначення, крім ESP |

| Масштаб | Немає (завжди 1) | 1, 2, 4, 8 |

| Зсув | 0, 8, 16 біт | 0, 8, 32 біт |

Як видно з таблиці, при 32-бітній адресації функціональне призначення регістрів МП фіксовано менш жорстко.

2. Класифікація і формати команд МП IA-32

Сукупність команд, що можуть бути виконані конкретним мікропроцесором, називається системою команд мікропроцесора.

Команда визначає операцію, яку має виконати МП над даними. Команда містить у явній або неявній формах інформацію про те, де буде розміщений результат операції, а також про адресу наступної команди. Обсяг, займаний командою в пам'яті, складає декілька байт і залежить від призначення команди. У загальному випадку формат команди містить операційну та адресну частини. Команди містять однобайтний або двохбайтний код інструкції, за яким можуть випливати декілька байт, що визначають режим виконання команди, і операнди (об'єкти, над якими або за допомогою яких виконується команда). Команди можуть використовувати від нуля до трьох операндів. Нагадаємо, що операнд – це об'єкт у вигляді значення даних, вмісту регістрів або вмісту комірок пам'яті, з яким оперує команда.

Система команд МП сімейства Іntel 80X86 містить кілька сотень інструкцій, що мають різне функціональне призначення.

Можна навести таку класифікацію команд МП сімейства Іntel 80X86:

- інструкції пересилання даних,

- інструкції введення-виведення,

- інструкції двійкової арифметики,

- інструкції десяткової арифметики,

- інструкції логічних операцій,

- зсуви й обертання (циклічні зсуви),

- інструкції обробки біт і байт,

- команди передачі керування,

- умовні переходи,

- інструкції виклику процедури,

- строкові операції,

- операції з прапорами,

- інструкції завантаження покажчиків,

- інструкції математичного співпроцесора,

- інструкції пакетів мультимєдійних розширень (MMX, SSE),