Дипломная работа: Мікропроцесорна метеостанція

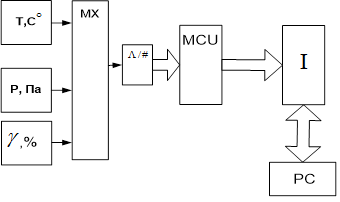

Рисунок 2 – структурна схема

Структурна схема представлена на рисунку 2 , за рішенням першого пункту є актуальна і складається з таких блоків:

Блок 1,2,3

- датчик температури, призначений для вимірювання температури повітря

- датчик тиску, призначений для вимірювання

тиску повітря

- датчик вологості, призначений для вимірювання вологості повітря

Блок 4, 5

- мультиплексор, призначений для керування потоками даних для вибору каналу за якими проводиться вимірювання та інших задач пов’язаних с керуванням потоками інформації.

- АЦП, призначений для перетворення відхідної безперервної величини в якій міститься вимірювальна інформація у цифровий код, який теж містить цю інформацію.

Блок 6

-Мікроконтролер, призначений для обробки вимірювальної інформації, яка переставлена у цифровому вигляді, керування потоками інформації, забезпечення обміну даними між окремими частинами ІВС та зовнішніми пристроями.

Блок 7

- Інтерфейс, призначений для обміну даними між зовнішніми пристроями.

Блок 8

- Персональний комп’ютер .

Три датчика вимірюють свої фізичні величини. На виході яких після вимірювання утворюється аналогова величина, яка подається через мультирлексор на АЦП. Який перетворює аналогову величину в цифровий код. Після цього цей код поступає на мікроконтролер. А потім через інтерфейс на ПК.[2]

3. Розробка електричної принципової схеми мікропроцесорної метеостанції

3.1 Вибір мікро контролера

Для реалізації задач дипломного проекту використовується 8-розрядний мікроконтролер фірми Atmel серії AT90S8515.

КМОН мікроконтролери AT90S8515 реалізовані по AVR RISC архітектурі (Гарвардська архітектура з роздільною пам'яттю і роздільними шинами для пам'яті програм і даних). Виконуючи команди за один тактовий цикл, прилади забезпечують продуктивність, що наближається до 1 MIPS/МГЦ.

AVR ядро об'єднує потужну систему команд з 32 8-розрядними регістрами загального призначення і конвеєрне звернення до пам'яті програм. Шість з 32 регістрів можуть використовуватися як три 16-розрядних регістра-покажчика при побічній адресації простору пам'яті. Виконання відносних переходів і команд виклику реалізується з прямою адресацією всього обсягу (4К) адресного простору. Адреси периферійних функцій містяться в просторі пам'яті вводу/виводу. Архітектура ефективно підтримує як мови високого рівня, так і програми на мовах асемблера.

Мікроконтролери містять: 4 Кбайт програмованого Flash, 128 байт СОЗП і 256 байт програмованого ЕСППЗП, 20 ліній вводу/виводу загального призначення, 32 регістри загального призначення, два таймера/лічильника з режимом захоплення і порівняння, 6-канальний 10-розрядний аналого-цифровий перетворювач, систему внутрішніх і зовнішніх переривань, програмований послідовний UART, програмований сторожовий таймер з внутрішнім генератором, послідовний порт з інтерфейсом SPI. Програмно управляються два режими енергозбереження. В пасивному режимі (idle) ЦПУ зупиняється, але СОЗУ, таймери/лічильники, порт SPI, сторожовий, таймер і система переривань залишаються активними. В стоповому режимі (power down) зупиняється тактовий генератор і, отже зупиняються всі функції, доки не надійде сигнал зовнішнього переривання або апаратного скидання,але зберігається вміст регістрів.

Вбудована Flash пам'ять програм може перепрограмовуватися безпосередньо в системі шляхом інтерфейсу SPI (в послідовному низьковольтному режимі) або програмуватися стандартними програматорами енергонезалежної пам'яті (в 12-вольтовому паралельному режимі).