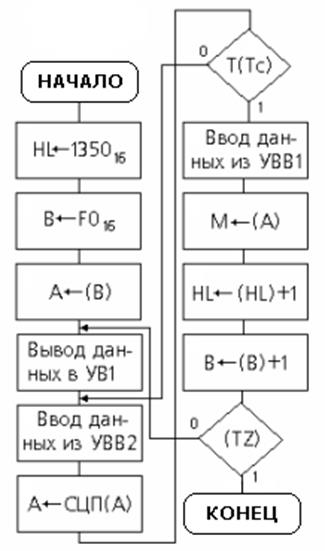

Дипломная работа: Устройство сбора информации

|

Недостатками данной системы по отношению к проектируемой являются следующие:

- процессор использует 3 источника питания: 5В, 12В, -5В

- морально устарела – программное обеспечение не отвечает требованиям настоящего времени, а именно: не совместим с IBM PC

Техническими достоинствами проектируемого устройства являются более широкие возможности, которые предоставляет МП комплект К1810, в частности, усовершенствованная система команд МП К1810ВМ86, более высокое быстродействие данной микросистемы, высокая точность снимаемых показаний.

Проектируемое устройство также отличается хорошими экономическими и эксплуатационными показателями, расчет которых произведен в третьей части дипломного проекта.

1.2 Логический расчет подсистем проектируемой системы

1.2.1 Проектирование подсистемы памяти

В функциональном отношении память делится программную и память данных. Память программ технически реализуется на БИС ПЗУ, память данных - на БИС ОЗУ. В некоторых случаях программная память может частично перекрывать память данных. Т.е. её реализация на БИС ОЗУ.

При проектировании запоминающих устройств микросистем решают задачи разработки требуемого объёма и разрядности ОЗУ и ПЗУ: распределение требуемого объёма памяти между ОЗУ и ПЗУ в адресном пространстве системы; создание аппаратного интерфейса сопряжения модулей ОЗУ и ПЗУ с системной магистралью.

Полупроводниковые БИС ЗУ характеризуются разрядностью хранимых данных и ёмкостью памяти - объёмом. Требуемая разрядность проектируемого ЗУ обеспечивается наращиванием разрядности путём соединения параллельно адресуемых БИС, а требуемый объём - наращиванием объёма путём соединения последовательно адресуемых субблоков, каждый из которых реализуется на конечном числе БИС ЗУ. Такой подход приемлем при построении модульной памяти данных и программ.

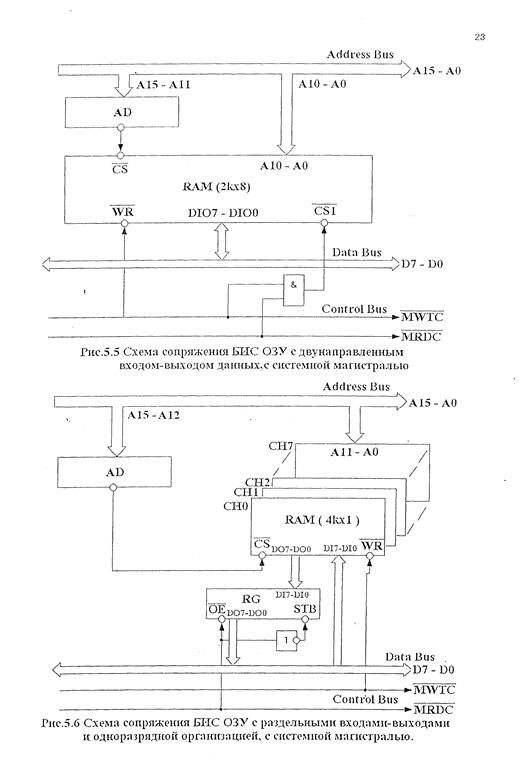

БИС ЗУ с двунаправленными выводами данных и раздельными шинами адреса и данных наиболее просто сопрягаются с системной магистралью микроЭВМ. Байтная организация БИС ёмкостью 2кВ ячеек избавляет от наращивания разрядности. Двунаправленный ввод - вывод данных исключает на пути между БИС ОЗУ и шиной данных вспомогательный буфер. Обычно локальная шина данных БИС ОЗУ имеет управляемое третье состояние. Примером данной организации служит БИС ОЗУ статического типа К541РУ2. Адресация ячеек памяти выполняется младшей частью адресов А10 —А0, Выборка кристаллов ОЗУ происходит старшими адресами А15 – A11. Адресный селектор AD (Address Decoder) может иметь. максимальное число выходов 32, а следовательно, может выбирать 32 БИС ОЗУ аналогичного типа. Этот блок ОЗУ полностью покрыл бы всё адресное пространство в 64кВ. Примечательно и то что дополнительный вход CS1, объединённый конъюнктивно со входом CSO, получает управление от ключа &, реализующего дизъюнкцию переменных командных сигналов чтения и записи памяти MRDC, MWTC с низким активным уровнем. Это в свою очередь активизирует БИС по выборке только в моменты чтения либо записи. При одноразрядной организации кристаллов памяти БИС производится наращивание чипов (Chip) СП i (i=7 - 0), как показано на рисунке 1.3.

|

|

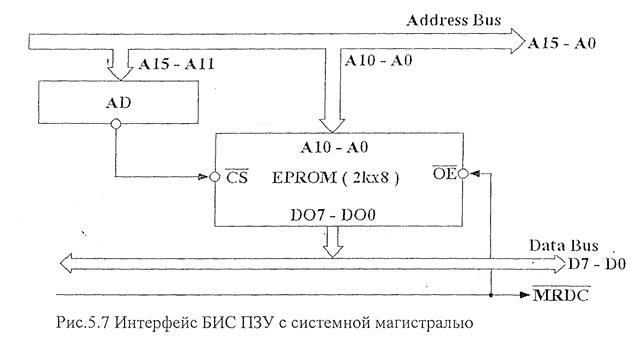

Раздельные входы-выходы данных требуют установки дополнительного буферного регистра, например КР580ИР82, разрешающего конфликтную ситуацию на шине данных. Как и ранее, адресный дешифратор выбирает блок ОЗУ ёмкостью 2кВ. На цикле чтения выбирается выходной буфер регистра. Благодаря инвертору формируется строб STB, что в свою очередь передаёт байт данных из выбранной ячейки через регистр на шину данных. При записи регистр заблокирован, а передаваемый байт из шины данных зафиксируется сигналом MWTC в выбранной ячейке. Организация интерфейса БИС ПЗУ с системной магистралью аналогично. Наиболее трудной задачей является проблема расчёта

адресного дешифратора.

Рисунок 1.5 Интерфейс БИС ПЗУ с системной магистралью

Для размещения модуля памяти заданной ёмкости, по заданному адресу необходимо определить функцию выборки CS конкретных БИС ЗУ в модуле памяти. Данную функцию лучше всего организовать применением ПЛМ ввиду простоты реализации и высокого быстродействия. В качестве ПЛМ применим БИС однократно программируемого ПЗУ К556РТ5. Оно имеет организацию 256х4 бит и открытый коллектор на выходах. В качестве ПЗУ применим БИС К573РФ5, а в качестве ОЗУ БИС К541РУ2. Рассчитаем функции селекции для каждой из них. Схема Электрическая принципиальная представлена в графической части дипломного проекта (Лист 1). Выходы Q2 – Q0 имеют открытый коллектор на выходах и подключены к шине +5В через подтягивающие резисторы. Именно они формируют выборку требуемого чипа памяти.

Для расчёта необходим стартовый адрес В и ёмкость С. Конечный адрес определяется по формуле:

Е=В+С-1

Необходим указатель шкалы р который определяется по формуле:

р=2(4i+j)

где i - младший значащий 16-ричный разряд

j - младший двоичный значащий разряд внутри i-го 16-ричного

Далее определим количество бит адреса G необходимых для адресации модуля памяти по формуле:

G=16 – log2 р

L - количество разрядов адресующих ячейки внутри БИС ЗУ.

Определяется по формуле: L=log2 C

Н - количество разрядов адресующих кристалл, определяется по формуле:

H=16-L