Доклад: Шини (Industrial Standard Architecture)

Шина PCI (Peripheral Component Interconnect bus)

Отже, переходимо до самого цікавого. Що ж знаходиться на сьогоднішній день усередині більшості наших комп'ютерів? Природно, шина PCI. Інше питання, чому саме ця шина. Спробуємо розібратися.

Отже, розробка шини PCI почалася навесні 1991 року як внутрішній проект корпорації Intel (Release 0.1). Фахівці компанії поставили перед собою ціль розробити недороге рішення, яке б дозволило цілком реалізувати можливості нового покоління процесорів 486/Pentium/P6 (от уже половина відповіді). Особливо підкреслювалося, що розробка проводилася "з нуля", а не була спробою установки нових "латок" на існуючі рішення. У результаті шина PCI з'явилася в червні 1992 року (R1.0). Розроблювачі Intel відмовилися від використання шини процесора і ввели ще одну "антресольну" (mezzanine) шину.

Завдяки такому рішенню шина вийшла, по-перше, процесоро-незалежною (на відміну від VLbus), а по-друге, могла працювати паралельно із шиною процесора, не звертаючи до неї за запитами. Наприклад, процесор працює собі з кешем або системною пам'яттю, а в цей час по мережі на вінчестер пишеться інформація. Просто здорово! Насправді ідилії, звичайно, не виходить, але завантаження шини процесора знижується здорово. Крім того, стандарт шини був оголошений відкритим і переданий PCI Special Interest Group, що продовжила роботу з удосконалювання шини (у даний час доступний R2.1), і в цьому, мабуть, друга половина відповіді на питання "чому PCI?"

Основні можливості шини наступні .

· Синхронний 32-х або 64-х розрядний обмін даними (правда, наскільки мені відомо, 64-розрядна шина в даний час використовується тільки в Alpha-системах і серверах на базі процесорів Intel Xeon, але, у принципі, за нею майбутнє). При цьому для зменшення числа контактів (і вартості) використовується мультіплексірування, тобто адреса і дані передаються по тим самим лініях.

· Підтримка 5V і 3.3V логіки. Рознімання для 5 і 3.3V плат розрізняються розташуванням ключів

· Частота роботи шини 33MHz або 66MHz (у версії 2.1) дозволяє забезпечити широкий діапазон пропускних здібностей (з використанням пакетного режиму):

· 132 МВ/хв при 32-bit/33MHz;

· 264 MB/хв при 32-bit/66MHz;

· 264 MB/хв при 64-bit/33MHz;

· 528 МВ/хв при 64-bit/66MHz.

При цьому для роботи шини на частоті 66MHz необхідно, щоб усі периферійні пристрої працювали на цій частоті.

· Повна підтримка multiply bus master (наприклад, кілька контролерів твердих дисків можуть одночасно працювати на шині).

· Підтримка write-back і write-through кеша.

· Автоматичне конфігуровання карт розширення при включенні харчування.

· Специфікація шини дозволяє комбінувати до восьми функцій на одній карті (наприклад, відео + звук і т.д.).

· Шина дозволяє встановлювати до 4 слотов розширення, однак можливе використання моста PCI-PCI для збільшення кількості карт розширення.

· PCI-пристрої обладнані таймером, що використовується для визначення максимального проміжку часу, у плині якого пристрій може займати шину.

При розробці шини в її архітектуру були закладені передові технічні рішення, що дозволяють підвищити пропускну здатність.

Шина підтримує метод передачі даних, називаний "linear burst" (метод лінійних пакетів). Цей метод припускає, що пакет інформації зчитується (або записується) "одним шматком", тобто адреса автоматично збільшується для наступного байта. Природним образом при цьому збільшується швидкість передачі власне даних за рахунок зменшення числа переданих адрес.

Шина PCI є тією черепахою, на якій коштують слони, що підтримують "Землю" - архітектуру Microsoft/Intel Plug and Play (Pn) PC architecture. Специфікація шини PCI визначає три типи ресурсів: два звичайних (діапазони пам'яті і діапазон уведення/висновку, як них називає компанія Microsoft) і configuration space - "конфігураційний простір".

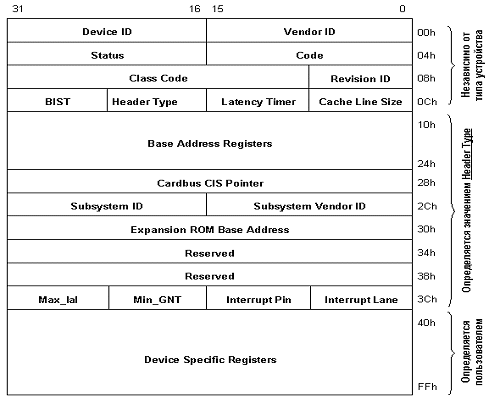

Конфігураційний простір складається з трьох регіонів:

· заголовка, незалежного від пристрою (device-independent header region);

· регіону, обумовленого типом пристрою (header-type region);

· регіону, обумовленого користувачем (user-defined region).

У заголовку утримується інформація про виробника і тип пристрою - поле Class Code (мережний адаптер, контролер диска, мультімедіа і т.д.) і інша службова інформація.

Наступний регіон містить регістри діапазонів пам'яті і введення/висновку, що дозволяють динамічно виділяти пристроєві область системної пам'яті й адресного простору. У залежності від реалізації системи конфігурація пристроїв виробляється або BIOS (при виконанні POST - power-on self test), або програмно. Базовий регістр expansion ROM аналогічно дозволяє відображати ROM пристрою в системну пам'ять. Поле CIS (Card Information Structure) pointer використовується картами cardbus (PCMCIA R3.0). З Subsystem vendor/Subsystem ID усі зрозуміло, а останні 4 байти регіону використовуються для визначення переривання і часу запиту/володіння.

Малюнок 4. Конфігураційний простір.