Контрольная работа: Арифметико-логическое устройство (АЛУ). Регистр PSW

Обозначение разрядов регистра TMOD приведено в таблице 3. Назначение разрядов регистра TMOD приведено в таблице 4.

Таблица 3

| Биты | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Обозн. | GATE1 | С/T1 | Ml.l | M0.1 | GATE0 | C/T0 | M1.0 | M 0.0 |

Таблица 4

| Биты | Наим енование | Назначение битов | М0-М1 | ||

|

0-1 | М0-М1 | Определяют один из 4-х режимов работы, отдельно для Т/С 1 и Т/С в | Все биты устанавливаются программно; биты 0-3 определяют | ||

| 4-5 | М 1 | М0 | Режим | режим работы Т/С в 0 | |

| 0 | 0 | 0 | режим работы Т/С 1. | ||

| 0 | 1 | 1 | |||

| 1 | 0 | 2 | |||

| 1 | 1 | 3 | |||

| 2,6 | С/Т 0 | Определяют работу в качестве: | |||

| С/ Т 1 | С/Т 0, С/Т 1 = 0 - таймера | ||||

| С/Т 0 , С/Т 1 = 1 - счетчика | |||||

| 3,7 | GATE | Разрешает управлять таймером от внешнего вывода ( INT0 - для Т/С 0, INT1 - дл я Т/С 1). GATE = 0 - управление запрещ ено GATE = 1 - управление разрешено | |||

При работе в качестве таймера содержимое регистра Т/С инкрементируется в каждом машинном цикле, т. е. Т/С является счетчиком машинных циклов ОМЭВМ, Поскольку машинный цикл состоит из 12 периодов частоты синхронизации ОМЭВМ fBQ , то частота счета в данном случае равна fBQ /1

При работе Т/С в качестве счетчика внешних событий содержимое регистра Т/С инкрементируется в ответ на переход из "1" в "0" сигнала на счетном входе ОМЭВМ (вывод Т0 для Т/С 0 и вывод Т1 для Т/С 1). Счетные входы аппаратно проверяются в фазе S5P2 каждого машинного цикла. Когда проверки показывают высокий уровень на счетном входе в одном машинном цикле и низкий уровень в другом машинном цикле, регистр Т/С инкрементируется. Новое (инкрементированное) значение заносится в регистр Т/С в фазе S3PI машинного цикла, непосредственно следующего за тем, в котором был обнаружен переход из "1" в "0" на счетном входе ОМЭВМ. Т. к. для распознавания такого перехода требуется два машинных цикла (24 периода частоты синхронизации ОМЭВМ fBQ ), то максимальная частота счета Т/С в режиме счетчика равна fBQ /24.

Чтобы уровень сигнала на счетном входе был гарантировано зафиксирован, он должен оставаться неизменным в течение как минимум одного машинного цикла.

Регистр управления (TCON) предназначен для приема и хранения кода управляющего слова. Обозначение разрядов регистра TCON приведено в табл. 9. Назначение разрядов регистра TCQN приведено в табл. 7.

Флаги переполнения TF0 и TFI устанавливаются аппаратно при переполнении соответствующих Т/С (переход Т/С из состояния "все единицы" в состояние "все нули"). Если при этом прерывание от соответствующего Т/С разрешено, то установка флага TF вызовет прерывание. Флаги TF0 и TFI сбрасываются аппаратно при передаче управления программе обработки соответствующего прерывания.

Флаги TF0 и TFI программно доступны и могут быть установлены/сброшены программой. Используя этот механизм, прерывания по TF0 и TFI могут быть вызваны (установка TF) и отменены (сброс TF) программой.

Флаги IЕ0 и IЕ1 устанавливаются аппаратно от внешних прерываний (соответственно входы ОМЭВМ INT0 и INT1) или программно и инициируют вызов программы обработки соответствующего прерывания. Сброс этих флагов выполняется аппаратно при обслуживании прерывания только в том случае, когда прерывание было вызвано по фронту сигнала. Если прерывание было вызвано уровнем сигнала на входе INT0 (INTI), то сброс флага IЕ должна выполнять программа обслуживания прерывания, воздействуя на источник прерывания для снятия им запроса.

Схема инкремента предназначена;

—для увеличения на 1 в каждом машинном цикле содержимого регистров Т/С 0, Т/С 1, для которых установлен режим таймера и счет разрешен;

— для увеличения на 1 содержимого регистров Т/С 0, Т/С 1, для которых установлен режим счетчика, счет разрешен и на соответствующем входе ОМЭВМ (Т0 для Т/С 0 и Т1 для Т/С 1) зафиксирован счетный импульс.

Схема фиксации INT0, INT1, Т0, Т1 представляет собой четыре триггера. В каждом машинном цикле в момент S5P2 в них запоминается информация с выводов ОМЭВМ INT0, INT1, Т0, Т1.

Схема управления флагами вырабатывает и снимает флаги переполнения Т/С и флаги запросов внешних прерываний.

Логика управления Т/С синхронизирует работу регистров Т/С 0 и Т/С 1 в соответствии с запрограммированными режимами работы и синхронизирует работу блока Т/С с работой ОМЭВМ.

Таблица 6

| Биты | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Обозначение | TF1 | TR1 | TF0 | TR0 | IЕ1 | IT1 | IЕ0 | IT0 |

Таблица 7

| Би-ты | Наименование | Назначение битов | Примечание |

| 6 | TR1 | Биты выключения Т/С, отдельно для | Биты устанавливаются и |

| 4 | ТR0 | Т/С в и Т/С 1. | сбрасываются программно. |

| TR=0 - выключен, | Доступны по чтению. | ||

| TR=1 - включен. | |||

| 7 | TF1 | Флаги переполнения Т/С. | Биты сбрасываются и |

| 5 | ТF0 | устанавливаются аппаратно | |

| и программно. | |||

| Доступны по чтению. | |||

| 2 | IT1 | Биты, определяющие вид прерывания | Биты устанавливаются и |

| 0 | IТ0 | по входам INT0, INT1: | сбрасываются программно |

| IТ=0 - прерывание по уровню | Доступны по чтению. | ||

| (низкому) | |||

| IТ=1 - прерывание по фронту | |||

| (переход из "1" в "0") | |||

| 3 | IE1 | Флаги запроса внешних прерываний, | Биты сбрасываются и устанавливаются аппа- |

| 1 | IE0 | по входам INT0, INT1 | ратно и программно. |

| Доступны по чтению. | |||

| Биты 4,5 относятся к Т/С в; биты 6, 7 - к Т/С 1. Биты 0,1 определяют внешние прерывания по входу INT0, биты 2,3 - по входу INT1. |

Режим работы каждого Т/С определяется значением битов М0, М1 в регистре TMOD. Т/С 0 и Т/С 1 имеют четыре режима работы. Режимы работы 0, 1, 2 одинаковы для обоих Т/С; Т/С 0 и Т/С 1 в этих режимах полностью независимы друг от друга. Работа Т/С 0 и Т/С 1 в режиме 3 различна. При этом установка режима 3 в Т/С 0 влияет на режимы работы Т/С 1.

Установка битов М0=0, М1=0 определяет режим работы 0. Т/С в режиме 0 представляет собой устройство на основе 13-разрядного регистра и функционально совместим с таймером/счетчиком семейства МК48 (восьмиразрядный таймер/счетчик с пред делителем на 32).

13-разрядный регистр состоит для Т/С 0 из 8 разрядов регистра ТН0 и 5 младших разрядов регистра TL0, а для Т/С 1—из 8 разрядов регистра ТН1 и 5 младших разрядов регистра TLI.

В этом режиме функцию делителя на 32 выполняют регистры TL0, TL1. Они являются программно доступными, но надо помнить, что значащими в режиме 0 являются только пять младших разрядов регистров TL0, TL1.

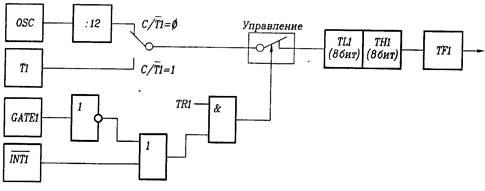

Для Т/С 0 логика работы аналогична. Источник синхронизации ОМЭВМ (внутренний или внешний). На выходе OSC — частота fBQ . Бит С/Т регистра TMOD определяет работу Т/С или в качестве таймера (С/Т=0), или в качестве счетчика (С/Т=1). Счет начинается при установке бита TR регистра Tcon в состояние "1". При необходимости управления счетом извне бит GATE регистра THOD устанавливается в состояние "1". Тогда при TR=1 счет будет разрешен, если на входе INT0 (для Т/С 0) или INTI (для Т/С 1) установленно состояние "1" и будет запрещен, если установлено состояние "0". Установка бита TR0 для Т/С 0 и TR1 для Т/С 1 в состояние "0" выключает Т/С независимо от состояния других битов.

При переполнении Т/С (переход содержимого регистра Т/С из состояния "все единицы" в состояние "все нули") устанавливается флаг TF0 для Т/С 0 или TF1 для Т/С 1 в регистре TCON.

Установка битов М1=0, М0=1 определяет режим работы 1. Режим 1 аналогичен режиму 0. Отличие состоит в том, что установка режима 1 превращает Т/С в устройство на основе 16-разрядного регистра. Для Т/С 0 регистр состоит из программно доступных пар TL0, ТН0, для Т/С 1 из программно доступных пар TL1, ТН1. Логика работы в режиме 1 на примере Т/С 1 показана на рис. 1.

Рис. 1. Логика работы Т/С 1 в режиме 1

Установка битов М1=1, М0=0 определяет режим В этом режиме Т/С представляет собой устройство на основе восьмиразрядного регистра TL0 для Т/С 0 и TLI для Т/С 1. При каждом переполнении TL0 кроме установки в регистре TCON флага TF0 происходит автоматически перезагрузка содержимого из ТН0 в TL0. Соответственно для Т/С 1 при переполнении TLI в регистре TCON устанавливается флаг TFI и происходит перезагрузка TLI из ТН1. Регистры ТН0 и ТН1 загружаются программно. Перезагрузка TL0 из ТН0 и TLI из ТН1 не влияет на содержимое регистров ТН0 и ТН1. Логика работы Т/С 0 в режиме 2 аналогична. Назначение битов управления TR0, TR1, GATE0, GATE1, С/Т 0, С/Т 1 такое же как режиме 0.