Контрольная работа: Преобразователь двоичного кода от 0 до 255 в двоично-десятичный код

3.3 Семисегментный индикатор с дешифратором

Для отображения результатов работы схемы воспользуемся семисегментными индикаторами. Они позволяют отображать цифры от 0 до 9, буквы от А до F, и десятичную точку. Значит, диапазон отображения такого индикатора – это число от 0 до F (HEX система исчисления).

Чтобы не задумываться о подключении дешифратора к индикатору, будем использовать микросхемы TIL309 производства фирмы TexasInstruments. В них уже встроен дешифратор, следовательно, на входы уже будет нужно подавать 4-разрядную шину данных.

Например, сигналу 1111 будет соответствовать число F

(81 + 41 + 21 + 11 = 1510 = F16 ).

Вход DP отвечает за десятичную точку. Именно его будем использовать для отображения совпадения/несовпадения кодов. Инверсный вход –LS отвечает за работу микросхемы, а инверсный вход –BI – за полное погашение циферблата.

При конструировании схемы будем использовать 3 таких семисегментных индикатора, так как на них будем выводить текущий 8-разрядный входной код.

4. СХЕМА ЭЛЕКТРИЧЕСКАЯ ПРИНЦИПИАЛЬНАЯ

Для реализации схемы электрической принципиальной нам понадобятся такие микросхемы и компоненты:

DD 1.. DD 3 – 3 микросхемы преобразователей кодов DM74185A.

HG 1.. HG 3 – 3 микросхемы семисегментных индикаторов с дешифратором TIL309. Используются для отображения входного кода .

SA 1 – микросхема SWD1-8. Микросхема имеет 8 позиций DIP-переключателей. Используется для установления двоичного кода.

R 1.. R 11 – резисторы по 10кОм.

Выводы на Землю и Питание +5В.

Сам чертеж схемы электрической принципиальной (А3) прилагается как приложение.

5. МОДЕЛИРОВАНИЕ СХЕМЫ В СРЕДЕ QUARTUS II

Для ввода двоичного кода используем 8 DIP-переключателей.

Так как в нашем распоряжении только 2 семисегментных индикатора, то будем оперировать входным кодом со старшими 8 разрядами равными 0. Тогда младшие 8 разрядов мы сможем наблюдать на индикаторах.

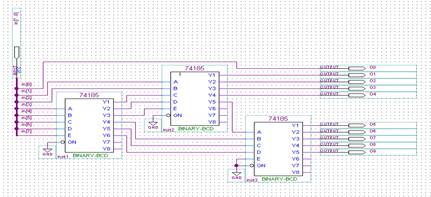

Схема для симуляции показана на рис. 5., ее временные диаграммы на рис. 6. Схема для загрузки на учебный стенд показана на рис. 7.

Рис. 5. Схема преобразователя двоичного кода от 0 до 255 в двоично-десятичный код.

Рис. 6. Временная диаграмма работы преобразователя двоичного кода от 0 до 255 в двоично-десятичный код.

Рис. 7. Схема преобразователя двоичного кода от 0 до 255 в двоично-десятичный код, подготовленная для загрузки на стенд.

Как видно с временных диаграмм, моя схема преобразовует двоичного код в двоично-десятичный код.

Имеется место задержкам на выходе ( задержки преобразователей кодов примерно вдвое превосходят задержки логических элементов).

ВЫВОДЫ

В данной расчетно-графической работе мною был реализован и исследован преобразователь двоичного кода от 0 до 255 в двоично-десятичный код.