Контрольная работа: Принцип побудови лінійних кодерів і декодерів

Побудова кодера безпосереднього зчитування (матричного кодера) основана на використанні кодового поля, на якому відображені усі ![]() можливі кодові групи для заданої розрядності коду (m). Реалізація матричного кодера можлива з використанням спеціалізованої електронно-променевої трубки, або набору

можливі кодові групи для заданої розрядності коду (m). Реалізація матричного кодера можлива з використанням спеціалізованої електронно-променевої трубки, або набору ![]() компараторів.

компараторів.

Схема матричного кодера на електронно-променевій трубці зображена на рис 2.

Рисунок 2

Пилоподібна напруга розгортає тонкий електронний промінь по горизонталі, а по вертикалі промінь переміщається АІМ сигналом, що кодується.

Кодування АІМ сигналу відповідного рівня виконується завдяки тому, що відхилений цим сигналом промінь „пробігає” по тому чи іншому рядку маски, попадає через отвори на колектор і відділяється на резисторі навантаження.

Наявність отворів відповідає кодовій таблиці, кожний рядок якої відображує рівень сигналу у двійковій системі лічення. Перевагою такого кодера є швидкодія, недоліком – необхідність використовувати для роботи високі напруги, невисока стабільність, висока вартість.

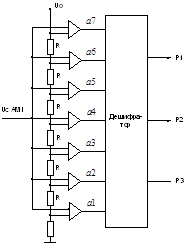

Схема кодера на компараторах для m=3 наведена на рис. 3.

|

Рисунок 3

Напруга ![]() є рівнем обмеження, яка подається на подільник з

є рівнем обмеження, яка подається на подільник з ![]() однакових резисторів, тому на входах компараторів діє відповідна опорна напруга. Значення

однакових резисторів, тому на входах компараторів діє відповідна опорна напруга. Значення ![]() відображують і-й рівень сигналу (

відображують і-й рівень сигналу (![]() ) причому різниця між

) причому різниця між ![]() та

та ![]() дорівнює кроку квантування

дорівнює кроку квантування ![]() , значення

, значення ![]() і відповідне значення розрядів сформованого паралельного коду Грея (P1,P2,P3) наведені в табл. 1

і відповідне значення розрядів сформованого паралельного коду Грея (P1,P2,P3) наведені в табл. 1

Таблиця 1

| Рівні АІМ сигналу | Значення коефіцієнтів | Вихідний код Грея | ||||||||

| Р1 | Р2 | Р3 | ||||||||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Досить легко визначити, що структура дешифратора визначається з використанням булевих функцій:

![]() ;

;

![]() ;

;

![]() .

.

У сучасних ЦСП використовують переважно кодери порозрядного зваження.

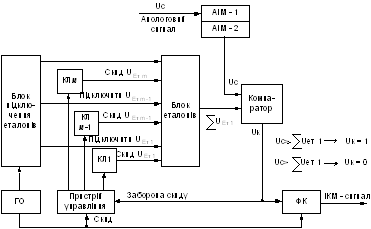

Структурна схема кодера порозрядного зваження наведена на рис. 4.

Аналоговий сигнал дискретизується і перетворюється в АІМ сигнал. На вхід компаратора (схеми порівняння) подається дискретний АІМ-сигнал, рівень якого за допомогою перетворювача АІМ-1 в АІМ-2 запам’ятовується на час кодування.

На другий вхід компаратора подається сума еталонних сигналів з блоку еталонів. Еталонні сигнали підключаються почергово, починаючи з максимального![]() , управляючими сигналами з блоку підключення еталонів.

, управляючими сигналами з блоку підключення еталонів.

Якщо![]() , то на виході компаратора формується сигнал, що призводить у свою чергу формування „1” на виході формувача коду (ФК). Підключений

, то на виході компаратора формується сигнал, що призводить у свою чергу формування „1” на виході формувача коду (ФК). Підключений ![]() не скидається, бо вихідний сигнал компаратора „Заборона скиду” забороняє скид.

не скидається, бо вихідний сигнал компаратора „Заборона скиду” забороняє скид.

На черговому такті кодування підключений ![]() сумується з еталонним сигналом

сумується з еталонним сигналом ![]() , після чого процес порівняння і формування значення чергового розряду кодової комбінації повторюється аналогічно розглянутому.

, після чого процес порівняння і формування значення чергового розряду кодової комбінації повторюється аналогічно розглянутому.

Рисунок 4

Якщо ж ![]() , то на виході компаратора сигнал відсутній, тому на виході ФК значення відповідного розряду дорівнює „0”. Сигналом „Скид” з генераторного обладнання еталон

, то на виході компаратора сигнал відсутній, тому на виході ФК значення відповідного розряду дорівнює „0”. Сигналом „Скид” з генераторного обладнання еталон ![]() відключається.

відключається.

Таким чином, сутність роботи кодеру полягає у тому, що:

– підбір суми еталонних сигналів, що приблизно дорівнює рівню вхідного сигналу, виконується за m кроків;

– еталони підключаються по черзі послідовно, починаючи із старшого ![]() ;

;

– на кожному і-му такті підключається черговий і-й еталон, а компаратор здійснює порівняння величини сигналу ![]() з сумою еталонів

з сумою еталонів  .

.

Якщо ![]() , то вихідний сигнал компаратора

, то вихідний сигнал компаратора ![]() , еталон

, еталон ![]() залишається підключеним, у відповідному розряді кодової групи на виході ФК формується „1”. Якщо ж

залишається підключеним, у відповідному розряді кодової групи на виході ФК формується „1”. Якщо ж ![]() , то вихідний сигнал компаратора

, то вихідний сигнал компаратора ![]() , еталон

, еталон ![]() відключається, на виході формувача коду (ФК) у відповідному розряді кодової групи формується пауза („0”).

відключається, на виході формувача коду (ФК) у відповідному розряді кодової групи формується пауза („0”).

Розглянемо процес кодування на конкретному прикладі. Припустимо,