Курсовая работа: Адаптер паралельного обмена

Рис. 2.1 – Выбранная структурная схема устройства

2.1.1 Назначение отдельных функциональных блоков.

2.1.1.1 Селектор адреса

Основной интерфейсной функцией, выполняемой УС, работающем в режиме программного обмена, является селектирование или дешефрирование адреса. Эту функцию выполняет узел, называемый селектором адреса, который должен выработать сигналы, соответствующие выставлению на шине адреса магистрали кода адреса, принадлежащего данному УС или одного из зоны адресов данного УС.

Самое простое решение при построении селектора адреса использование только микросхем логических элементов. Основным достоинством такого подхода является высокое быстродействие (задержка не превышает 30нс). При использовании микросхем с малыми входными токами можно обойтись без буферов.

Но есть и недостаток этой схемы: необходимость проектирования схемы заново для каждого нового адреса, сложность организации выбора нескольких адресов.

Если необходимо иметь возможность изменять выбираемый адрес, то можно предусмотреть использование отключаемых инверторов для всех линий адреса. Тогда, подключая или отключая нужные инверторы с помощью перемычек или переключателей, получаем возможность перестраивать селектор адреса в некоторых пределах.

|

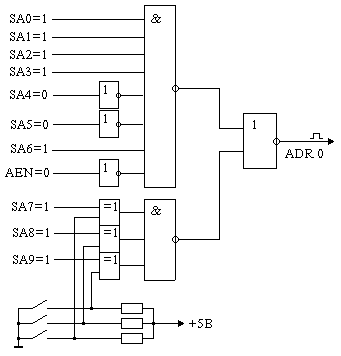

Рис. 2.2 – Селектор адреса с изменяемым адресом |

Другой путь – применение элементов "Исключающее ИЛИ", работающих как управляемые инверторы. На рисунке 2.2 показан селектор адреса, выбирающий в зависимости от кода на шине AS, задаваемого перемычками, адреса 3CFh, 2CFh, 1CFh и так далее (всего 8 различных адресов).

2.1.1.2. Буфер данных

Для буферирования наиболее часто используются микросхемы магистральных приемников, передатчиков и приемопередатчиков, называемые буферами.

Электрическая развязка подразумевает обеспечение нужных входных и выходных токов (уровни на ISA - ТТЛ).

Передатчики должны обеспечивать большой выходной ток и высокое быстродействие. Часто они должны иметь также отключаемый выход (для шины данных), то есть иметь выход с открытым коллектором или с тремя состояниями на выходе. Это связано с необходимостью перехода устройства в пассивное состояние в случае отсутствия обращения к нему.

Передатчики часто выполняют функцию мультиплексирования данных, которые должны поступать на шину данных ISA от различных источников.

2.1.1.3 Блок CPU .

Блок содержит однокристальный микроконтроллер, который выполняет функции выработки внутренних управляющих стробов. Применен ОМК типа PIC16C64.

3 РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА

3.1 Блок регистров

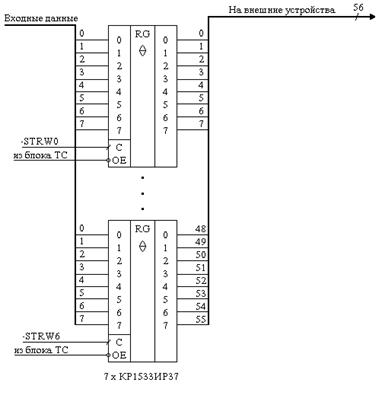

Выходные сигналы формируются регистрами с тремя состояниями выхода КР1533ИР37, каждый из которых может находиться в активном или пассивном состоянии в зависимости от значения соответствующего бита в управляющем слове (блок CPU).

Управляющие сигналы операционной части используются для записи выходных данных (-STRW0...STRW6).

Схема блока регистров и блока буферов приведена на рисунке 3.1.

3.2 Блок приема данных (от ВУ)

Для чтения состояний внешних линий используются однонаправленные буфера КР1533АП5, выходы которых объединяются для мультиплексирования читаемых данных.

Управляющие сигналы операционной части используются для чтения входных данных (-STRR0...-STRR6).

Схема блока приема данных изображена на рисунке 3.2

Рис. 3.1 – Схема блока регистров

3.3 Блок прерываний