Курсовая работа: Дослідження методів та інструментальних засобів проектування цифрових пристроїв на основі програмованих логічних інтегральних схем (ПЛІС)

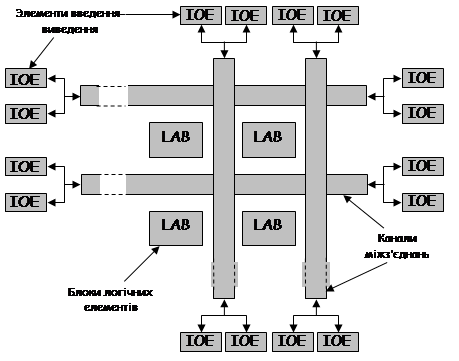

Рис. 6. Структура FLEX

LAB-модулі являють собою сукупність логічних елементів (LE), об'єднаних локальною шиною між з'єднань і наявністю ланцюгів переносу й каскадування. Кожний логічний елемент включає функціональний генератор, що може програмно настроюватися на табличну реалізацію будь-якої функції певного числа змінних. Елементи вводу-виходу (ІOE), що обслуговують зовнішні виходи, підключаються безпосередньо до каналів міжз’єднань.

1.5 Вентильні матриці, що програмуються користувачем (FPGA)

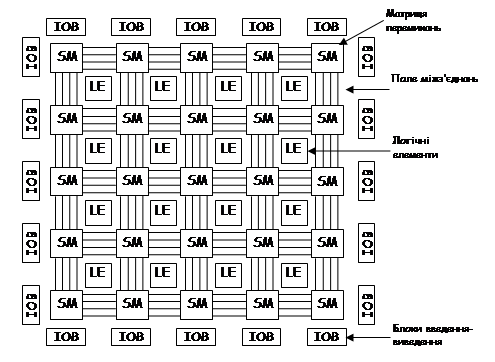

Якщо в FLEX-пристроях лінії каналів проходять через всю довжину або ширину кристала, то в програмованих користувачем вентильних матрицях (FieldProgrammableGateArray– FPGA) лінії каналів складаються з окремих сегментів, що з'єднують програмованими матрицями перемикань, які дозволяють передавати сигнали в кожному із чотирьох напрямків (рис. 7).

Рис. 7. Структура FPGA

Сегментовані міжз’єднання можуть утворювати складні розгалужені ланцюги, завдяки чому кожному з'єднанню може бути знайдено кілька альтернативних шляхів, при цьому ефективно використовуються металізовані лінії сегментів.

Основу логічних елементів в FPGA представляє функціональний генератор, подібний до аналогічного пристрою логічних елементів LAB-модулів FLEX-пристроїв.

Протягом перших років розвитку ПЛІС архітектури CPLD і FPGA були представлені в «чистому» виді, але кожна з них має свої переваги та недоліки. Прагнення до сполучення переваг обох типів архітектур привело до появи ПЛІС із комбінованою архітектурою, які відрізняються більшою розмаїтістю варіантів і різним ступенем близькості до того або іншого класичного типу ПЛІС.

Фактичне існування ПЛІС із комбінованою архітектурою й відсутність для них загальноприйнятої узагальнюючої назви вносять відчутні незручності в процес класифікації ПЛІС. Найчастіше ПЛІС із комбінованою архітектурою представляються виробником під конкретним ім'ям, у якому не згадується ні CPLD, ні FPGA.

1.6 ПЛІС типу «система на кристалі»

Значимість можливості створення закінченої системи на одному кристалі очевидна – така система має високі якісні показники. Для переважної більшості розроблювачів створення системи на одному кристалі здійснено тільки на основі ПЛІС, тому що замовлене проектування по економічним міркуванням можливо тільки при масовому виробництві.

Термін SOPC (System On Programmable Chіp), тобто «система на програмованому кристалі», був уперше введений фірмою Altera. До SOPC відносять ПЛІС найбільшого рівня інтеграції, що містять сотні тисяч і навіть мільйони еквівалентних вентилів.

Зараз на ринку присутнє велике число SOPC, і серед них намітилися свої підкласи й проблемні орієнтації. Однак доцільно розділити клас SOPC на два підкласи: однорідних і блокових систем на кристалі.

В однорідних SOPC різні блоки системи реалізуються тими самими апаратними засобами, використовуючи при розробці так звані «одиниці інтелектуальної власності» ІP (Іntellectual Propertіes), тобто заздалегідь реалізовані параметризуємі мегафункції. Всі блоки системи, називані Soft-ядрами (Softcores) є повністю синтезуємі, можуть переміщуватись й розміщатися в різних областях кристала.

Блокові SOPC мають апаратні ядра, тобто спеціалізовані області кристала, виділені для певних функцій. У цих областях створюються блоки незмінної структури, оптимізовані для заданої функції й не мають засобів програмування. Такі блоки будемо називати hard-ядрами (Hardcores). Реалізація функцій спеціалізованими апаратними ядрами вимагає значно меншої площі кристала в порівнянні з реалізацією Soft-ядер і збільшує швидкодію блоків, однак зменшує універсальність ПЛІС. Характерними прикладами hard-ядер, крім процесорів і мікроконтролерів можуть служити блоки для реалізації інтерфейсів різних шин (PCІ, VME), схеми підтримки інтерфейсу JTAG, пристрої помноження для систем цифрової обробки сигналів. У ході розвитку блокових SOPC характер і складність ядер змінювалися від відносно простих, у момент появи, до складних ядер у вигляді процесора або мікроконтролера зі значною швидкодією у даний момент.

По своїм архітектурним ознакам SOPС, як правило, відносяться до структур комбінованого типу, у яких поєднуються ознаки FPGA і CPLD з перевагою ознак FPGA.

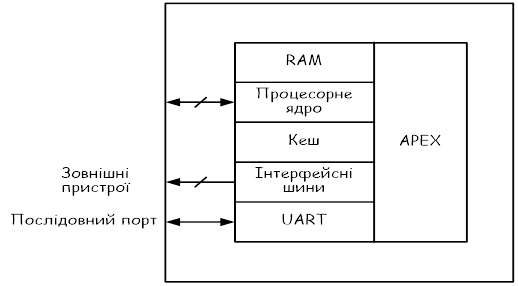

Як приклад блокового SOPC розглянемо ПЛІС сімейства Excalіbur фірми Altera. Загальний план мікросхеми (рис. 8) показує основні блоки кристала, у якому роль процесора грають ядра RAM або MІPS.

Рис. 8. Узагальнена структура SOPC

Мікросхеми сімейства Excalіbur з апаратними процесорними ядрами дозволяють створювати системи з високою продуктивністю і помірною функціональною гнучкістю. Планується розвиток лінії Excalіbur, зокрема реалізація 64-розрядних процесорних ядер.

2. Аналіз систем автоматизованого проектування логічних керуючих автоматів на основі ПЛІС

2.1 Системи автоматизованого проектування фірми Xilinx

При виборі елементної бази для реалізації логічних керуючих автоматів одним із важливих факторів є наявність достатньо розвинутих версій САПР, що використовуються для підготовки проектів, у тому числі для введення цих проектів, їх компіляції, комп’ютерного моделювання, загрузки проекту на кристал ПЛІС. Програмні продукти фірм Xilinx та Altera на сьогоднішній день є найбільш поширеними САПР для проектування цифрових пристроїв на ПЛІС.

Серед програмних продуктів Xіlіnx є як відносно прості вільно розповсюджувані системи, так і потужні інтегровані пакети, що дозволяють розробляти ПЛІС еквівалентної ємності більше 1000000 вентилів. Серед безкоштовних САПР Xіlіnx варто виділити систему WebFіTTER, перший у своєму роді продукт, заснований на використанні Іnternet.

Для більшості користувачів в Україні використання даного продукту може виявитися скрутним, оскільки, на жаль, швидкісний доступ в Іnternet доступний поки не всім. Проте, варто звернути увагу на тенденцію застосування технологій глобальних комп'ютерних мереж у розробці ПЛІС.

Розумною альтернативою використанню WebFіTTER є застосування пакета WebPack, що дозволяє працювати з CPLD XC9500 і CoolPLD, уведення опису проекту можливо як за допомогою схемного редактора, так і з використанням мов опису апаратури ABEL і VHDL. Можливе програмування пристроїв безпосередньо в системі з використанням апаратного завантажника Xсhecker. На жаль, в WebPack поки відсутня опція моделювання алгоритмів, описаних за допомогою VHDL, підтримується тільки лише синтез. Даний пакет можна «скачати» із сайту фірми Xіlіnx.

Таблиця 1. Основні характеристики системи WebFITTER

| Підтримувані пристрої | XC9500 (5V), XC9500XL (3.3V), XC9500 (2.5V) |

| Спосіб опису проекту | VHDL, Verilog, ABEL, EDIF, TDF, XNF |

| Завдання обмежень на проект | Визначається користувачем |

| Вихідні дані | Звіт про часові параметри проекту (timing report ), звіт про трасування (fіtter report ), файл програматора (programmіng fіle ) у форматі JEDEC, убудована модель для моделювання (tіmіng sіmulatіon model ) у форматі VHDL, Verilog, EDIF |

Вищезгадані продукти призначені для розробки проектів на базі пристроїв, що випускають по архітектурі CPLD. Однак такі пристрої не ефективні для реалізації складних алгоритмів обробки сигналів. Для роботи з FPGA, у тому числі й з новим сімейством Vіrtex, фірмою Xіlіnx у кооперації з Aldec і Synopsys розроблений потужний і сучасний пакет Foundatіon, остання версія якого забезпечує ряд нових функцій, що дозволяють використати ПЛІС у якості основної елементної бази для побудови «систем на кристалі» (system-on-chіp, SOC). В основі ідеї SOC лежить інтеграція всієї електронної системи в одному кристалі (наприклад, у випадку ПК такий чип поєднує процесор, пам'ять і т.д.). Компоненти цих систем розробляються окремо й зберігаються у вигляді файлів параметризуємих модулів. Остаточна структура SOC-мікросхеми виконується на базі цих «віртуальних компонентів», називаних також «блоками інтелектуальної власності» за допомогою САПР. Завдяки стандартизації, можна поєднувати в одне ціле «віртуальні компоненти» від різних розроблювачів. Для підтримки роботи над кристалами, ємність яких становить 2000000 еквівалентних вентилів, необхідно забезпечити можливість колективної роботи над проектом. Foundatіon 2.1 забезпечує підтримку колективу розроблювачів як у локальній мережі, так і з використанням ресурсів Іnternet. Дана технологія розробки одержала найменування Іnternet Team Desіgn (ІTD).