Курсовая работа: Исследование арифметико–логического устройства для выполнения логических операций

Арифметико-логическое устройство функционально можно разделить на две части:

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

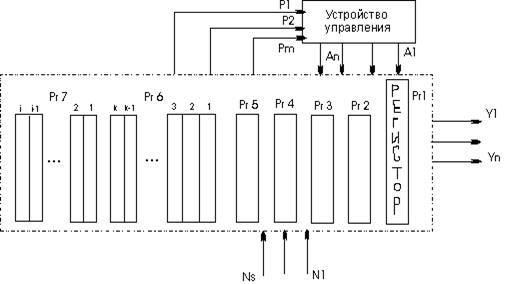

Рисунок. 1 Структурная схема АЛУ

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация, поступающая из оперативной или пассивной памяти N1, N2, ...NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма, которая записывается в виде последовательности микрокоманд A1,A2, ..., Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2,..., Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2,..., рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, ...,уs, в ОЗУ. Функции регистров, входящих в АЛУ: Рг1 – регистр (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений; Рг2, РгЗ - регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции); Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата; Ргб - k индексных регистров, содержимое которых используется для формирования адресов; Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся: сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется не сколько различных операций пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

2. ОПИСАНИЕ БЛОКА РЕГИСТРА

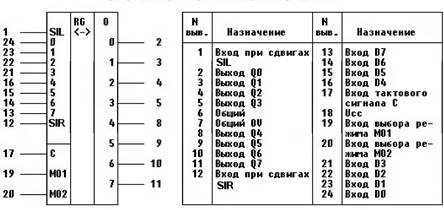

В задании используются универсальные регистры, разрядность которых (n) можно определить по количеству выходов. В регистре к1500ир141 имеется 4 выходов следовательно разрядность регистра (n) будет равна 4 Микросхема к1500ир141 представляет собой регистр, состоящий из 4 D-тиггеров. Выходы М01 и М02 позволяют выбрать один из четырех режимов работы регистра: загрузка данных, хранение данных, сдвиг данных в лево или в право. Все операции (кроме хранения) происходят по положительному перепаду на тактовом входе С. Регистр имеет 2 последовательных входа SIL (вход данных для сдвига в право) и SIR (вход данных для сдвига влево). При напряжении высокого уровня на входах М01 и М02 регистр хранит данные независимо от сигналов на других входах. Условно графическое обозначение микросхемы к1500ир141 представлено на рисунке 2.

Рисунок 2-Условно графическое обозначение микросхемы к1500ир141 и обозначение входов и выходов

Для данной микросхемы существуют 2 способа записи информации последовательный и параллельный. При последовательном способе записи сигнал V должен быть низкого уровня, а код, который записывается, должен поступать на вход D0. С каждым тактовым импульсом М01 входной код продвигается на один разряд в сторону старшего разряда. При параллельном способе записи код подается на входы D4-D1. Запись проводится в паузе между тактовыми импульсами М01 при V=1 импульсом М02. Если после записи число нужно сдвинуть, то регистр переводят в режим сдвига сигналом V=0 и руководят с помощью импульсов М01. При условии, что Q1 - выход младшего разряда, а Q4 - старшего, информация в регистре сдвигает влево (обратной сдвиг). Но он может быть преобразован и в регистр со сдвигом вправо (прямой сдвиг). Для этого необходимо выполнить следующие внешние соединения: D3 с Q4, D2 с Q3, D1 с Q2. Код записывают по входу D4 при V = 1, а руководят регистром тактовыми импульсами М02. Таким образом, в рассмотренном регистре выполняются условия как прямого, так и обратного сдвигов. Регистр имеет выходы от всех разрядов, что позволяет считывать записанный код как в последовательной, так и в параллельной формах представления информации во времени.

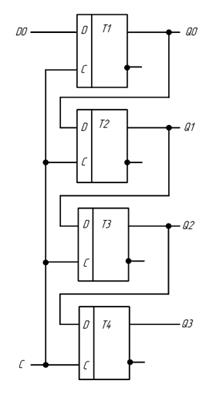

Рисунок 3 – Логическая схема регистра к1500ир141

Регистр к1500ир141 является универсальными (регистр общего назначения), он может использоваться для временного хранения любых данных, при этом позволять работать как с регистром целиком, так и отдельно и с каждой его половиной, (регистры АН, ВН, СН, DH -- старшие (High) байты, а регистры AL, BL, CL, DL -- младшие (Low) байты, соответствующих двухбайтовых регистров). Но также универсальный регистр к1500ир141 может использоваться и как специальный при выполнении некоторых конкретных команд программы.

В данной работе требуется рассчитать сигналы на выходе микросхемы к1500ир141 после подачи на вход двоичного сигнала 1110 при сдвиге влево на 4 разряда. При сдвиге влево происходит смещение операнда на более уровень а на его место устанавливается сигнал 0. Процесс сдвига показан в таблице 2.

Таблица 2 – процесс сдвига влево на 4 разряда.

Вход триггера Q4 Q3 Q2 Q1

Число сдвига 1 1 1 0

Число сдвига 1 1 1 0

Число после 1-го сдвига 1 1 0 0

Число после 2-го сдвига 1 0 0 0

Число после 3-го сдвига 0 0 0 0

Число после 4-го сдвига 0 0 0 0

Результатом сдвига будет двоичное число 0000.

3. ПРОЕКТИРОВАНИЕ СУММАТОРА

Параллельные четырехразрядных сумматоры предназначены для одновременного суммирования двух четырехразрядных чисел и характеризуются различными способами передачи сигналов переноса от младших разрядов сумматора к старшим.