Курсовая работа: Логічні елементи, що застосовуються в електронно-обчислювальній техніці

0

0

1

1

0

1

0

1

0

0

1

1

Тут Qt означає логічний рівень на прямому виході до подачі імпульсу синхронізації, a Qt+1 - логічний рівень на цьому виході після подачі імпульсу синхронізації.

В такому тригері відбувається затримка сигналу на виході по відношенню до сигналу, поданого на вхід, під час паузи між синхросигналами. Для стійкої роботи тригера необхідно, щоб протягом синхроімпульса інформація на вході була незмінною.

Тактові D-тригери можуть бути з потенційним і динамічним управлінням. У перших з них інформація записується протягом часу, при якому рівень сигналу С= 1. В тригерах з динамічним управлінням інформація записується тільки протягом перепаду напруги на вході синхронізації. Динамічні входи зображають на схемах трикутником. Якщо верхівка трикутника звернута в сторону мікросхеми, то тригер «спрацьовує» по фронту вхідного імпульсу, якщо від неї - по зрізу імпульсу. В такому тригері інформація на виході може бути затримана на один такт по відношенню до вхідної інформації.

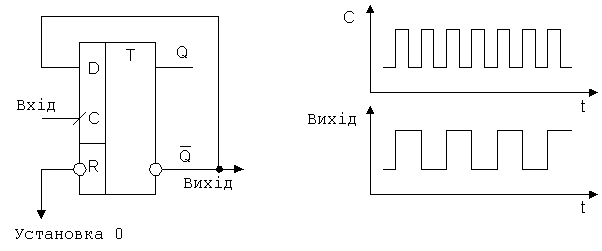

Лічильний Т-тригер (рисунок 6). Його називають також тригером зі лічильним входом. Він має один вхід керування Т і два виходи Q і Q' . Інформація на виході такого тригера змінює свій знак на протилежний при кожному позитивному (або при кожному негативному) перепаді напруги на вході. В серії мікросхем, що випускаються, Т-тригерів, як правило, немає. Але тригер такого типу може бути створений на базі тактового D-тригера, якщо його інверсний вихід з'єднати з інформаційним входом. Як видно з діаграми, частота сигналу на виході Т-тригера в два разу нижче частоти сигналу на вході, тому такий тригер можна використовувати як подільник частоти і двійковий лічильник.

Рисунок 6 - Лічильний тригер

В серіях мікросхем, що випускаються, є також універсальні JK-тригери. При відповідному під'єднанні вхідної логіки JK-тригер може виконувати функції тригера будь-якого іншого типу.

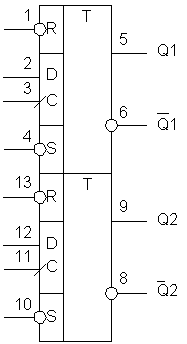

Умовні графічні позначення тригерів на принципових схемах наведені на рисунку 7.

Рисунок 7 - Графічні позначення тригерів

3 РЕГІСТРИ

Кілька тригерів можна об'єднати в регістр - вузол для зберігання чисел з двійковим поданням цифр розрядів. Основними видами регістрів є паралельні і послідовні (зсувні).

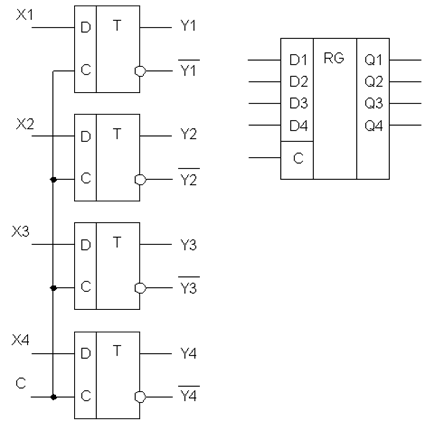

В паралельному регістрі на тактових D-тригерах (рисунок 8) код числа, що запам‘ятовується, подається на інформаційні входи всіх тригерів і записується в регістр з приходом тактового імпульсу. Вихідна інформація змінюється з подачею нового вхідного слова і приходом наступного імпульсу запису. Такі регістри використовують в системах оперативної пам'яті. Число тригерів в них дорівнює максимальній розрядності слів, що зберігаються у ньому.

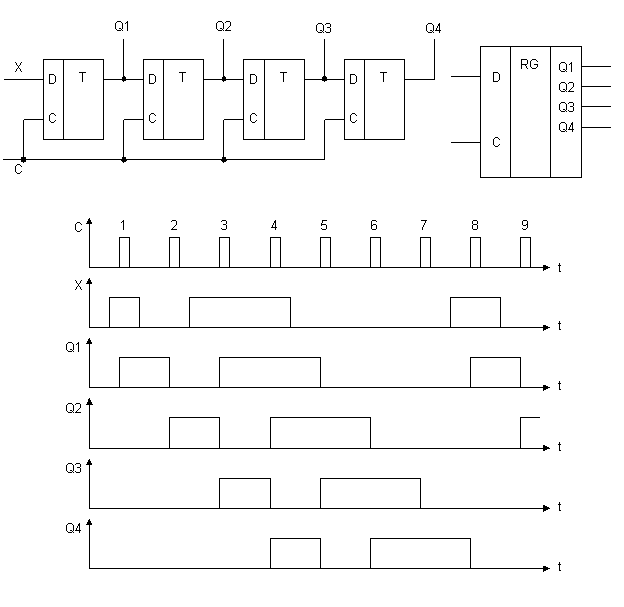

Схема послідовного регістра і часова діаграма, що ілюструє його роботу, наведені на рисунок 9. З приходом тактового імпульсу С перший тригер записує код Х (0 або 1), що знаходиться в цей момент на його вході D, а кожний наступний тригер перемикається в стан, в якому до цього знаходився попередній. Так відбувається тому, що сигнал, який записується, проходить із входу D тригера до виходу Q із затримкою, більшою тривалості фронту тактового імпульсу (протягомі якого відбувається запис). Кожний тактовий імпульс послідовно зсуває код числа у регістрі на один розряд. Тому для запису N-розрядного коду необхідно N тактових імпульсів. На діаграмі видно, що чотирирозрядне число 1011 було записане у відповідні розряди регістра (1 - Q4, 0 - Q3, 1 - Q2, 1 - Q1) після приходу четвертого тактового імпульсу. До приходу наступного тактового імпульсу це число зберігається в регістрі у виді паралельного коду на виході Q4-Q1. Якщо необхідно отримати інформацію, що зберігається у послідовному коді, то її знімають із виходу Q4 в моменти приходу наступних чотирьох імпульсів (5-9). Такий режим називається режимом послідовного зчитування.

Рисунок 8 - Паралельний регістр на тактових D-тригерах

Дуже зручні універсальні регістри, що дозволять здійснювати як послідовний, так і паралельний запис і зчитування. Такі регістри можна використовувати як перетворювачі паралельного коду в послідовний і навпаки. Наприклад, мікросхема К555ИР1 (рисунок 10) - чотирирозрядний універсальний зсувний регістр. Регістр працює в режимі зсуву по тактових імпульсах, що надходять на вхід С1, якщо на вході V2 є напруга низького рівня. Вхід V1 служить для введення інформації в перший розряд регістра в цьому режимі. Якщо ж на вході V2 напруга високого рівня, то регістр здійснює паралельний запис інформації із входів D1-D4 по імпульсах синхронізації, що надходять на вхід С2.