Курсовая работа: Мікропроцесорний АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується

До складу процесора крім лічильника команд (PC), арифметико-логічного пристрою (ALU) і блоку регістрів загального призначення (GPR) входять:

регістр стану мікроконтролера SREG;

регістр-показник стека SP чи SPL і SPH.

Високопродуктивно AVR ALU з'єднано безпосередньо з усіма 32 швидкодіючими регістрами загального призначення. За один тактовий цикл ALU виконує операцію між регістрами цього реєстрового файлу. Операції ALU підрозділяються на три основні категорії: арифметичні, логічні і бітові [8].

2.2 Вибір додаткових елементів

Структурна схема АЦП порозрядного врівноваження містить в аналоговій частині «надлишковий» ЦАП, що використовується під час перетворення.

Число розрядів ![]() , задіяних у надлишковому ЦАП, природно, більше ніж у двійковому

, задіяних у надлишковому ЦАП, природно, більше ніж у двійковому ![]() й визначається зі співвідношення:

й визначається зі співвідношення:

![]() . (2.1)

. (2.1)

Так, для побудови АЦП 14-ти розрядної точності (![]() =14) при α=1,618 потрібен ЦАП на

=14) при α=1,618 потрібен ЦАП на ![]() =20 розряду коду "золотої пропорції". Незважаючи на збільшення розрядної сітки, швидкодія АЦП на основі НПСЧ не зменшується, а навпаки, може бути істотно збільшена. Зазначений ефект виникає внаслідок витрати частини надмірності ваг розрядів на автокомпенсацію динамічних похибок із сигналу, що компенсує [8].

=20 розряду коду "золотої пропорції". Незважаючи на збільшення розрядної сітки, швидкодія АЦП на основі НПСЧ не зменшується, а навпаки, може бути істотно збільшена. Зазначений ефект виникає внаслідок витрати частини надмірності ваг розрядів на автокомпенсацію динамічних похибок із сигналу, що компенсує [8].

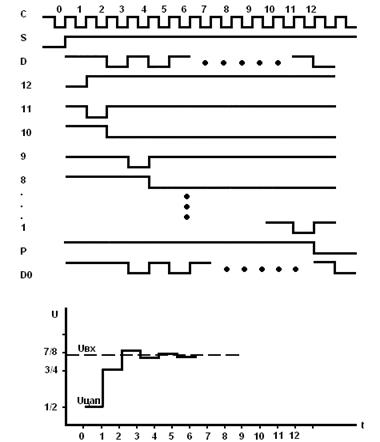

Для роботи ЦАП використовується РПН, що забезпечує утворення кодових комбінацій, які створюють компенсуючий сигнал для компаратора в процесі порозрядного врівноваження. Основною складовою РПН є спеціальний регістр – мікросхема AM2504 [7], яка зображена на рисунку 2.2, яка призначена для побудови АЦП, що працюють по принципу послідовного наближення з числом розрядів до 12. Має в своєму складі 4 входи:

С – для подачі тактових імпульсів (спрацювання по зростанню тактових імпульсів), D – інформаційний вхід, Е – дозвіл перетворення та S – вхід “пуск“.

Робота мікросхеми показана на діаграмах C-DO, що зображена на рисунку 2.2.

Рисунок 2.2 – Мікросхема AM2504

При подачі на вхід S логічного 0 по спаду чергового імпульсу відбувається початкова установка тригерів регістра. На виході закінчення перетворення C0 з'являється логічна 1. Такий стан регістра зберігатиметься до тих пір, поки на вході S буде логічний 0.

Після встановлення на вході S логічної 1 перший спад імпульсу негативної полярності виробить запис в тригер регістра з виходами 12 і 12 інформації з входу D і встановить вихід 11 в стан 0, на виходах 10-1 і C0 буде логічної 1.

Спад чергового імпульсу негативної полярності виробить запис інформації з входу D в черговий тригер регістра і встановить наступний за ним вихід в стан 0. Таким чином, на виходах регістра по черзі з'являється логічний 0, вслід за ним - інформація з входу D.

Після запису інформації з входу D в останній тригер регістра (з виходом 1) на виході C0 з'являється логічний 0 і цей стан регістра фіксується до появи логічного 0 на вході S. Якщо вхід S з'єднати з виходом C0, поява логічного 0 на виході C0 по спаду чергового тактового імпульсу приведе до встановлення початкового стану регістра аналогічно імпульсу 0. В результаті мікросхема повторюватиме описаний вище цикл роботи.

Рисунок 2.3 – Часова діаграма роботи мікросхеми AM2504

Наявність входу Е дозволяє сполучати між собою мікросхеми для отримання регістрів послідовного наближення на більшу кількість розрядів, як показано на рисунку 2.4. Робота таких регістрів аналогічна роботі однієї мікросхеми.

Мікросхема дозволяє використовувати її як регістр послідовного наближення і з меншим, ніж на 12, числом розрядів, для чого для подачі сигналу на вхід S можна використовувати його з'єднання з будь-яким з виходів 1-11.

Рисунок 2.4 – З’єднання мікросхем AM2504 для збільшення кількості розрядів

2.3 Розробка загального алгоритму функціонування АЦП

АЦП порозрядного врівноваження перетворить аналоговий сигнал в цифровий за N кроків, де N — розрядність АЦП. На кожному кроці визначається по одному біту шуканого цифрового значення, починаючи СЗР і закінчуючи МЗР. Послідовність дій за визначенням чергового біта полягає в наступному. На ЦАП виставляється аналогове значення, утворене з бітів, вже визначених на попередніх кроках; біт, який повинен бути визначений на цьому кроці, виставляється в 1, більш молодші біти встановлені в 0. Отримане на допоміжному ЦАП значення порівнюється з вхідним аналоговим значенням. Якщо значення вхідного сигналу більше значення на допоміжному ЦАП, то визначуваний біт отримує значення 1, інакше 0. АЦП цього типу володіють одночасно високою швидкістю і хорошою розрядністю.

Слід зазначити, що використання АЦП із ЦАП на основі НПСЧ у складі систем цифрової обробки аналогових сигналів також дає певні переваги перед двійковими перетворювачами інформації. Так, зменшений час врівноважування дозволяє підняти частоту дискретизації, збільшити кількість оброблюваних каналів при роботі в багатоканальному режимі. Незважаючи на спрощену технологію виготовлення аналогових вузлів, результуюча точність перетворення як ЦАП, так і АЦП на основі НПСЧ може бути досить високою при роздільності не менше 14-16 двійкових розрядів. Це досягається, зокрема, калібруванням ваг розрядів і корекцією статичних похибок, що здійснюється цифровим обчислювальним пристроєм. Причому даний пристрій може одночасно виконувати дві функції: калібрування похибок і перетворення НПСЧ у двійкову систему. Для виконання операцій безпосередньо з цифровими сигналами доцільно використовувати мікроконтролер. СП, a-ЦАП, РПН і БК сукупно складають ядро АЦП – блок порозрядного врівноважування (БПВ). У БК передбачено можливість подачі сигналу керування Узв.

Задачею БПВ є перетворення аналогового сигналу з виходу ПВЗ в робочий код К(а), що формується у РПН. Для перетворення робочого коду К у двійковий код використовується окремий ЦОП. Причому на етапі виготовлення системи і компонування аналогових вузлів здійснюється високоточне вимірювання ваг розрядів АЦП. Отримані результати у вигляді двійкових кодів заносяться в БП і використовуються надалі для роботи. Для зв’язку ЦОП із каналами виведення двійкової цифрової інформації використовується послідовний або паралельний інтерфейс залежно від необхідної швидкості передавання інформації [9].

Граф-схему алгоритму функціонування АЦП системи наведено в додатку А. Тут: j – номер каналу; i – номер такту порозрядного врівноважування в БПВ; k – номер дискретизації; С – результат обчислень у ПК; В – операнд, якому призначаються значення кодів із ПЗП; К(ΔА0) – код похибки нуля; Кi – код ваги i-го додатного розряду; ![]() – код ваги i-го від’ємного розряду. Причому у випадку НПСЧ (0,1) існує тільки один від’ємний розряд – знаковий; П – масив пам'яті в мікроконтролері, в якому фіксуються коди дискретизованих відліків аналогових сигналів. Значення цифрового сигналу у=1 відповідає режимові вибірки ПВЗ, у=0 - збереження. У процесі функціонування системи аналогові сигнали з входу подаються на ПВЗ. Дискретизовані відліки потім перетворюються в цифрові еквіваленти і надходять у ЦОП для відповідного оброблення. Причому на етапі проектування виміряються ваги розрядів a-ЦАП, коди яких фіксуються в ПЗП. Надалі ці розряди вважаються "точними" і "стабільними". Водночас варто відзначити, що зазначений пристрій можна виконати, зокрема, на базі мікроконтролера.

– код ваги i-го від’ємного розряду. Причому у випадку НПСЧ (0,1) існує тільки один від’ємний розряд – знаковий; П – масив пам'яті в мікроконтролері, в якому фіксуються коди дискретизованих відліків аналогових сигналів. Значення цифрового сигналу у=1 відповідає режимові вибірки ПВЗ, у=0 - збереження. У процесі функціонування системи аналогові сигнали з входу подаються на ПВЗ. Дискретизовані відліки потім перетворюються в цифрові еквіваленти і надходять у ЦОП для відповідного оброблення. Причому на етапі проектування виміряються ваги розрядів a-ЦАП, коди яких фіксуються в ПЗП. Надалі ці розряди вважаються "точними" і "стабільними". Водночас варто відзначити, що зазначений пристрій можна виконати, зокрема, на базі мікроконтролера.