Курсовая работа: Микропроцессорная системы отображения информации

Все действия ЦП заранее запрограммированы и подчинены последовательности команд, хранимой в ПЗУ. Кроме того, в ПЗУ записаны необходимые для работы константы, например, формы знаков. Для хранения вводимой информации и программ необходима оперативная память (ОЗУ).

Устройство ввода/вывода предназначено для ввода информации в систему и вывода обработанной информации на индикацию.

Селектор адреса предназначен для выбора одного из внешних устройств.

МП синхронизируется тактовыми импульсами, формируемыми ТГ. Для тактирования используется двухфазная система импульсов C1 и C2, а максимальная тактовая частота МП составляет 2МГц.

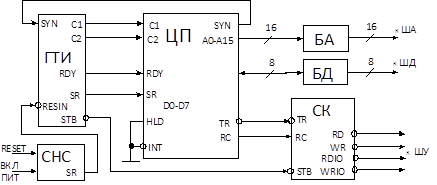

Разработаем функциональная схема центрального процессора.

Функциональная схема центрального процессора представлена на рисунке 2.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Рисунок 2 – Функциональная схема центрального процессора

Рисунок 2 – Функциональная схема центрального процессора

При включении питания или при нажатии клавиши "Reset", система начального сброса (СНС) формирует сигнал "Установка нуля", который поступает на вход генератора тактовых импульсов (ГТИ) "RESIN". ГТИ формирует сигнал "SR", поступающий на одноименный вход ЦП, что обеспечивает автоматическую установку микропроцессора в исходное состояние.

ГТИ, формирует сигналы C1 и C2 – тактовые сигналы с различными фазами; RDY – сигнал "Готовность"; STB – стробирующий сигнал состояния, формируемый при наличии на входе "SYN" напряжения высокого уровня, поступающего с выхода микропроцессора в начале каждого машинного цикла. Сигнал "STB" используется для занесения информации состояния МП в системный контроллер для формирования управляющих сигналов.

Так как к шине адреса может быть подключено большое число внешних устройств, а выходные линии канала адреса не обладают достаточной нагрузочной способностью, то в схему необходимо ввести буферные устройства шины адреса (БА). Для увеличения нагрузочной способности шины данных используется буфер данных (БД).

Для формирования управляющих сигналов используется системный контроллер (СК). От МП в СК подаются сигналы: TR– выдача информации; RC – прием информации.

СК формирует следующие управляющие сигналы: RD – чтение памяти; WR – запись в память; RDIO – чтение из устройства ввода/вывода; WRIO – запись в устройство ввода/ вывода.

Так как МП работает по опросу, то выводы МП "INT" и "HLD" заземляются. В случае, если МП СОИ работает по прерываниям, то подается уровень логической единице.

Разработаем функциональная схему блока запоминающих устройств

Функциональная схема блока запоминающих устройств представлена на рисунке 3.

Рисунок 3 – Функциональная схема блока запоминающих устройств

Входы ПЗУ и ОЗУ A0 – А10 подключены к младшим адресам шины адреса. На входы выборка кристалла (CS) подаются сигналы с СА. На вход RD ПЗУ подается сигнал RD с системного контроллера и по низкому уровню этого сигнала данные по указанному адресу передаются на ШД. На вход WR/RD ОЗУ подается сигнал WR с СК и по низкому уровню этого сигнала данные передаются на ШД.

Разработаем функциональную схема селектора адреса.

Функциональная схема селектора адреса представлена на рисунке 4.

Рисунок 4 – Функциональная схема блока селектора адреса

Селектор адреса представляет собой устройство управления другими устройствами системы. С ША адрес поступает на вход СА, а на выходе получаем сигнал выборки устройства из числа, входящих в систему.

МП КР580ВМ80А может адресовать до 256 устройств ввода-вывода и обеспечить адресацию внешней памяти объемом 65536 байт.

Распределение адресного пространства представлено в таблице 1.

| Двоичный адрес | Адрес | Устройство | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (HEX) | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0000 | Начальный адрес ПЗУ |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 07FF | Конечный адрес ПЗУ |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0800 | Начальный адрес ОЗУ |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0FFF | Конечный адрес ОЗУ |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1000 | Начальный адрес ПККИ |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1001 | Конечный адрес ПККИ |

Таблица 1 – Распределение адресного пространства системы

Селектор адреса спроектируем с помощью логических элементов на основе распределенного адресного пространства.

Для блока запоминающих устройств на линиях A12-A15 находятся логические нули, а линия A11 управляет выборкой ПЗУ (A11=0) или ОЗУ (A11=1). Такое включение позволяет объединить оба запоминающих устройства в едином адресном пространстве объемом 4Кбайта, причем ПЗУ располагается в области 0000H – 07FFH, а ОЗУ в области 0800H – 0FFFH. Такое расположение удобно тем, что после установки в исходное состояние, процессор начинает выборку команд с адреса 0000H, где и располагается ПЗУ, содержащее основную программу.