Курсовая работа: Преобразователи напряжение-ток

![]() . (15)

. (15)

При выполнении условия:

![]() (16)

(16)

второе слагаемое в выражении (15) обращается в нуль, поэтому результирующая крутизна преобразования напряжения в ток не будет зависеть от уровня входного сигнала.

Так как выражение (15) было получено при определённых допущениях (например, a всех транзисторов не зависят от тока и равны единице), выполнение условия (14) не исключает полную независимость крутизны от уровня входного напряжения. Однако погрешность преобразования можно сделать достаточно малой, что подтверждается результатами моделирования рассмотренных схем (рис. 6).

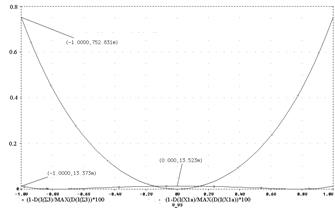

Графики, приведённые на рисунке 6, по сути, представляют собой отклонение в процентах нормированной крутизны прямой передачи от единицы, что при U0 = 1 совпадает с выражением (8). Для схемы рисунка 2а максимальное отклонение составляет 0,75 %, а для схемы ПНТ рисунка 5 – не превышает 0,015 %.

Рис. 6. Графики, иллюстрирующие отклонение от линейности схем ПНТ рисунка 2а (¯) и ПНТ рисунка 5 (□)

Следует также отметить, что для схемы ПНТ, приведённой на рисунке 5, достаточно точное выражение для отклонения от линейности может быть получено из выражений (13) и (14) после аппроксимации их полиномами четвёртой степени. В этом случае можно дать следующие рекомендации. Условие (16) даёт приближённое значение сопротивлений резисторов R1 и RK, а дальнейшую параметрическую оптимизацию можно осуществить, добиваясь, чтобы значения отклонения на краях диапазона совпадали со значение отклонения в точке UX = 0. Это будет наилучшее приближение к линейной функции [21].

Некоторый недостаток схемы ПНТ (рис. 5) – наличие четырёх идентичных источников тока, которые, с одной стороны, повышают энергопотребление схемы, с другой – их неидентичность нарушит выполнение условий компенсации нелинейности во всём диапазоне входных напряжений.

Отметим, что для качественной работы подобных схем ПНТ важна абсолютная идентичность (симметричность) каналов усиления для положительных и отрицательных приращений входного сигнала.

Дабы уйти от необходимости использовать четыре согласованных источника тока, можно воспользоваться способом, реализованным в схемах ПНТ, приведённых на рисунках 7 и 8 [22, 23].

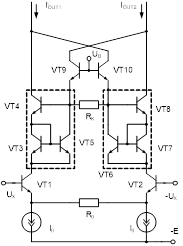

Рис. 7. Схема высоколинейного ПНТ с делителями тока в коллекторной цепи для компенсации нелинейной составляющей крутизны преобразования

Работу схемы рисунка 7 можно пояснить следующим образом. Транзисторы VT1 и VT2 образуют дифференциальный каскад, который с помощью резистора R0 осуществляет преобразование входного напряжения в ток коллекторов названных транзисторов. В коллекторные цепи транзисторов VT1 и VT2 включены делители тока на транзисторах VT3, VT4, VT5 и VT6, VT7, VT8 (обведены пунктиром на рисунке 7).

Делители тока представляют собой токовое зеркало Вильсона, которое питается «снизу» от источника тока, поэтому ток коллектора транзистора VT1 (VT2) перераспределяется между транзисторами VT4 и VT5 (VT8 и VT6) в зависимости от отношения площадей эмиттеров транзисторов VT3 и VT5 (VT7 и VT6).

Таким образом, часть тока, пропорциональная входному напряжению UX, ответвляется с помощью делителей тока, и на транзисторах VT9 и VT10 выделяется разность напряжений база-эмиттер, являющаяся функцией приращения выходного тока IX. С помощью резистора RК формируется компенсирующий ток, так что разносное приращение токов на выходе можно представить выражением:

![]() , (17)

, (17)

где К < 1 – коэффициент деления в делителях тока.

Третье слагаемое в правой части выражения (17) и есть компенсирующий ток. Очевидно, что, если выполнить условие:

![]() ,

,

слагаемые, содержащие логарифм, обращаются в нуль, в результате крутизна прямого преобразования:

![]() , (18)

, (18)

что несколько меньше, чем в базовой схеме ПНТ (рис. 2а), в связи с чем К рекомендуется выбирать меньше 0,5 (например 0,1…0,2).

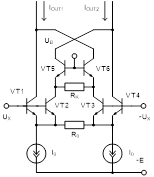

Схожей по принципу действия оказывается схема ПНТ (рис. 8). Здесь делитель тока выполнен непосредственно в дифференциальном каскаде, а принцип формирования компенсирующего тока аналогичен предыдущему случаю.

Рис. 8. Схема высоколинейного ПНТ с делителями тока в дифференциальном каскаде для компенсации нелинейной составляющей крутизны преобразования

Отметим, что в этом случае выбором площадей эмиттеров пар транзисторов VT1 и VT2 (VT3 и VT4) коэффициент деления Кi опорного тока I0 для соответствующего плеча дифференциального каскада выбирается из условий:

![]() ,

,