Курсовая работа: Проектирование цифрового сглаживающего фильтра

0ВН – Порт С (Порт обработки сигнала квитирования)

0СН – Регистр хранения таймера (младший байт)

0DH - Регистр хранения таймера (старший байт)

Адресное пространство памяти, исходя из её объёма, распределено следующим образом:

![]()

Настройка таймера

Таймер используется для формирования последовательности импульсов следующих с частотой дискретизации. В качестве входного сигнала счётчика используется выход тактовых импульсов микропроцессора.

Для обеспечения частоты дискретизации 1.2 КГц коэффициент счёта таймера должен равняться:

![]()

![]()

Запись управляющего слова осуществляется в два регистра таймера старший и младший, микросхемы РУ55.

Загрузка управляющего слова производится в порты

C9HПорт ОD- старший байт

C4HПорт ОС- младший байт

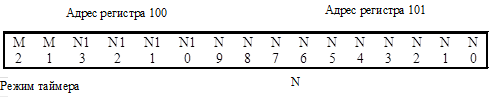

Функционирование таймера. Блок таймера содержит 14-битовый вычитающий счетчик, 16-битовый регистр хранения, схему формирования выходного сигнала и схему управления таймером. Счетчик выполняет основную функцию данного блока, заключающуюся в подсчете импульсов, поступающих извне на вход TIMERIN. Регистр хранения в 14 младших битах содержит коэффициент счета N, который загружается в него при подготовке таймера к работе и задает начальное состояние счетчика. Число N может иметь любое значение от 2Н до 3FFFN. Два старших бита этого регистра составляют регистр режима (RR), в котором хранится код ТМ2ТМ1 заданного режима работы таймера. Схема формирования обеспечивает форму сигнала TIMEROUT в соответствии с режимом работы таймера. Этот сигнал обязательно изменяет свое значение в момент окончания счета. Схема управления реализует заданный режим работы таймера и, в частности, осуществляет перезагрузку числа N из регистра в счетчик при организации циклической (непрерывной) работы таймера. Программирование таймера состоит в загрузке двухбайтового слова в регистр хранения, после чего осуществляется запуск счетчика с помощью специальной команды (предусмотрен только программный запуск таймера). Во время работы счетчик уменьшает свое содержимое по фронту каждого импульса, поступающего на вход TIMERIN. Когда требуется производить отсчет реального времени, этот вход обычно соединяется с выходом PCLK генератора. При обращении к таймеру используются два адреса: младший байт N загружается по адресу А2А1АО = 101, старший — по адресу А2А1АО=101. Это позволяет загружать указанные байты в любом порядке.

Формат двухбайтового слова, загружаемого в таймер, представлен на рисунке.

Рис. 1 Формат команды управления таймером

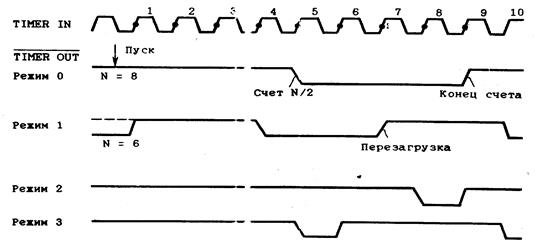

Два старших бита М2М1 задают один из четырех режимов работы таймера, при которых вырабатываются соответствующие сигналы на выходе TIMEROUT (рис. 6.56), В режиме 0 поддерживается выходной сигнал TIMEROUT = 1 в течение первой половины счета и TIMEROUT —0 в течение второй. При нечетном N первый полупериод счета, соответствующий высокому уровню выходного сигнала, оказывается на единицу больше второго. Режим 1 аналогичен режиму 0 с той разницей, что каждый раз по окончании счета производится автоматическая перезагрузка N из регистра хранения в счетчик и повторный запуск счетчика. Таким образом, таймер работает в непрерывном режиме деления на N частоты повторения входных импульсов и генерирует выходной сигнал симметричной формы (скважность равна двум). В режиме 2 после окончания счета формируется одиночный импульс напряжения низкого уровня, длительность которого равна одному периоду входных (счетных) импульсов. Режим 3 отличается от режима 2 автоматической перезагрузкой и перезапуском счетчика, что обеспечивает непрерывность работы таймера. Это режим деления частоты с выработкой выходного сигнала несимметричной формы (скважность зависит от значения N).

Рис .2 Временная диаграмма работы таймера

Таблица 3: Режимы работы таймера

| Режим работы таймера | НАИМЕНОВАНИЕ РЕЖИМА |

| 0 | Ждущий мультивибратор с программным запуском |

| 1 | Делитель частоты, генератор меандра |

| 2 | Делитель частоты, генератор импульсов несимметричной формы |

| 3 | Генератор задержанного строба |

Для нашего случая таймер использует третий режим работы.

Таким образом, управляющее слово таймера будет иметь следующий вид ![]()

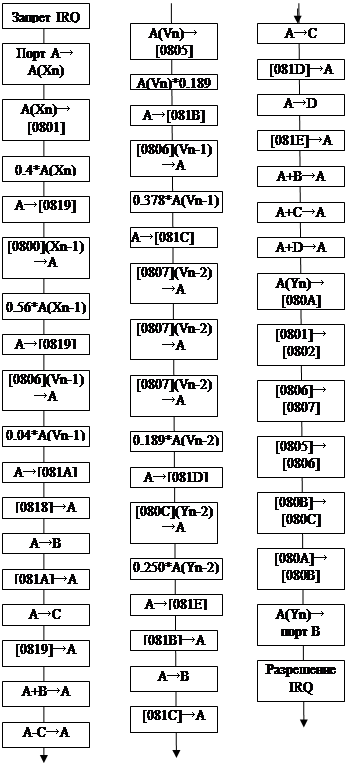

Алгоритм основной программы

Обоснование аппаратной части устройства

Набор К1821 определяет типовой состав аппаратных средств, образующих структуру вычислительного ядра системы. В его состав входят МП, ОЗУ, ПЗУ, схемы формирования сигналов синхронизации, микросхемы формирования сигналов управления системой. Полная структурная схема МП- устройства получается при объединении структуры вычислительного ядра и дополнительных аппаратных узлов.

Аппаратный состав фильтра в целом уже определен, незатронутым остается преобразователь ток-напряжение. Также следует произвести согласование адресов ОЗУ, ПЗУ, портов ввода-вывода с адресами МП.