Курсовая работа: Проектування комбінаційних схем на мікросхемах різного ступеню інтеграції

![]() ; - правило подвійного заперечення.

; - правило подвійного заперечення.

Число груп змінних також не повинне перевищувати р. У протилежному випадку зазначені перетворення виконують стосовно груп змінних. Такі перетворення дозволяють представити задану функцію в операторній формі з урахуванням числа входів елементів. Отримана в цьому випадку форма не буде нормальною, тому що за рахунок додаткового каскадування елементів комбінаційна схема буде містити більш двох рівнів.

На заключному третьому етапі по операторним представленнях функцій будується комбінаційна схема. Задана система елементів дозволяє реалізувати одне чи більше операторних представлень функції. Наприклад, при наявності елементів І, АБО і І-НІ можна використовувати в якості вихідної одну з п'яти нормальних форм (І/АБО, І-НІ/І-НІ, АБО/І-НІ, І-НІ/І, АБО/І) для одержання відповідних операторних представлень з урахуванням числа входів елементів. Для вибору однієї схеми з декількох можливих необхідно порівнювати їх по заданих параметрах. Найбільше часто такими параметрами є складність і швидкодія схем.

Існують кілька способів оцінки складності:

складність по Квайну (К), обумовлена як сумарне число входів усіх логічних елементів;

складність у числі логічних елементів М;

складність у числі умовних корпусів мікросхем:

,

,

де r — число типів мікросхем; mi — кількість мікросхем i-го типу; ni — число висновків мікросхеми i-го типу. У якості умовного використовується корпус мікросхеми на 14 виводів.

Параметри К и М доцільно використовувати при проектуванні інтегральних схем, тому що їхня вартість залежить від площі кристала, що пропорційна числу логічних елементів і числу їхніх входів. Оцінка N зручна при порівнянні складності пристроїв, побудованих на мікросхемах.

Швидкодія КС залежить від тимчасових параметрів логічних елементів t01 і t10 , що характеризують затримку сигналів елементом (час переходу вихідного сигналу від одного логічного рівня до іншого). На практиці використовують звичайно усереднене значення часу затримки t = (t01 + t10 )/2 чи максимальне t* = max (t01 , t10 ).

Наприклад, для КС на однотипних елементах середній час затримки сигналів визначається як T = Lt, де L — рівень схеми, дорівнює числу елементів, що входять у максимальну по довжині ланцюжок елементів. Якщо використовуються елементи з різною затримкою, то в схемі визначається шлях, що вимагає максимального часу поширення сигналів.

Рис 1.2

Вибирається з декількох можливих КС, що краще інших задовольняє заданим параметрам.

Проектування КС з багатьма виходами відрізняється тим, що система перемикальних функцій піддається спільній мінімізації, а потім перетворюється до операторного представлення таким чином, щоб число використовуваних логічних елементів було мінімальним.

При реалізації перемикальних функцій у ряді випадків можна зменшити кількість корпусів мікросхем, використовуючи мікросхеми середнього ступеня інтеграції, наприклад, дешифратори і мультиплексори.

Оскільки дешифратор на п входів реалізує всі констітуенти одиниці, то для реалізації перемикальної функції від п змінних досить за допомогою АБО елемента одержати диз'юнкцію констітуент одиниці тих наборів, на яких функція приймає одиничні значення. Якщо дешифратор має інверсні виходи, то відповідно до правила де Моргана замість АБО елемента варто використовувати елемент І-НІ.

Наприклад, функцію ![]() , представлену в ДДНФ, можна реалізувати за допомогою трьох входового дешифратора з прямими (рис. 1.2, а) чи інверсними (рис. 1.2, б) виходами.

, представлену в ДДНФ, можна реалізувати за допомогою трьох входового дешифратора з прямими (рис. 1.2, а) чи інверсними (рис. 1.2, б) виходами.

Якщо з кожної констітуенти можна винести за дужки змінну, то при наявності в дешифратора (стробуючого) входу Е знадобиться дешифратор з меншим числом інформаційних входів. Представивши останню з розглянутих функцій у вигляді ![]() , можна реалізувати її з використанням двухвходового дешифратора (рис. 1.2, в).

, можна реалізувати її з використанням двухвходового дешифратора (рис. 1.2, в).

Дешифратори найбільше доцільно використовувати при реалізації систем перемикальних функцій. У цьому випадку для побудови схем потрібно один дешифратор і стільки логічних елементів, скільки функцій містить система.

Мультиплексор з N інформаційними входами і k = log2 N керуючими входами дозволяє виключити k з п змінних перемикальної функції, представивши її через залишкові функції, кожна з яких залежить не більш ніж від n-k змінних.

Так, після двохкратного застосування леми про розкладення больової функції по змінній, функція y = f(xn ,…,x1 ) може бути представлена у формі

де f0 , f1 , f2 , f3 — залишкові функції від n–2 перемінних. Схема, що відповідає такому представленню функції, показана на рис. 1.3.

Залишкові функції можуть бути реалізовані будь-яким способом. Зокрема, кожна з них може бути представлена через свої статочне функції з використанням мультиплексоров. У кожнім конкретному випадку необхідно оцінювати складність схем при чи тім іншому способі реалізації функції. Помітимо, що складність схем залежить від того, які перемінні виключаються. Для одержання найбільш простої схеми може знадобитися перебір усіх комбінацій включаюдчи перемінних.

При реалізації функції від чотирьох перемінних з використанням мультиплексора, що має два керуючі входу (рис. 1.4), треба виключити шістьох різних пар перемінних (x4 x3 , x4 x2 , x4 x1 , x3 x2 , x3 x1 , x2 x1 ,). При виключенні кожної пари перемінних діаграму Вейча заданої функції можна розглядати як чотири самостійні діаграми для залишкових функцій f0 , f1 , f2 , f3 .

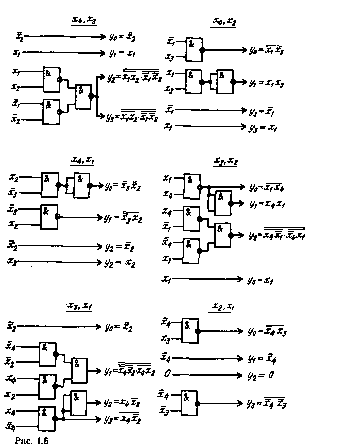

На рис. 1.5 показані всі шість варіантів визначення залишкових функцій. Виключає перемінні зазначені біля діаграм для кожного варіанта. Схеми на елементах І-НІ, що відповідають кожному варіанту, представлені на рис. 1.6. Найбільш проста реалізація заданої функції є при виключенні за допомогою мультиплексора перемінних х1 і х2 (рис. 1.7).