Курсовая работа: Розробка технічних засобів обміну інформацією для банківської системи з визначенням та виправленням помилок

![]()

![]()

![]()

![]()

![]()

![]() Основними сигналами управління є: WR, RD, C/D, CS. Вхідні сигнали WR та RD визначають напрямок потоку інформації, що передається з шини даних мікропроцесора до УСАПП чи навпаки. Вхідний сигнал C/D разом із сигналами WR, RD та CS визначає вид інформації, що поступає до мікросхеми чи до каналу даних.

Основними сигналами управління є: WR, RD, C/D, CS. Вхідні сигнали WR та RD визначають напрямок потоку інформації, що передається з шини даних мікропроцесора до УСАПП чи навпаки. Вхідний сигнал C/D разом із сигналами WR, RD та CS визначає вид інформації, що поступає до мікросхеми чи до каналу даних.

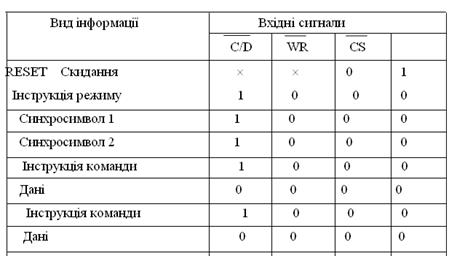

Послідовність записування інструкції команди та інструкції режиму, синхросимволів та даних для запуску мікросхеми наведена у таблиці 3.1. При цьому синхросимвол може бути один чи обидва взагалі відсутні, що визначається інструкцією режиму.

Таблиця 3.1 - Послідовність завантаження УСАПП

З таблиці 3.1 видно, що безпосередньо після скидання потрібно записати інструкцію режиму, тобто до регістра режиму записується перше слово управління для синхронного чи асинхронного режиму.

Оскільки в технічному завданні на курсовий проект задано асинхронний режим передачі, то слово управління буде мати вигляд, наведений на рис.3.1:

Рисунок 3.1 - Формат інструкції для асинхронного режиму

Відповідно до наведенної структури виберемо формат слова управління, наведений у табл. 3.2:

Таблиця 3.2 - Формат слова управління

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

Розряди D0 та D1 визначають асинхронний режим. Це поле також визначає швидкість приймання та передавання інформації, яку ми вибираємо рівною 1:1.

Розряди D2 та D3 визначають довжину (кількість бітів даних) слова, що передається чи приймається.

Розряди D4 та D5 здійснюють управління контролем парності. Біт контроля парності додається до бітів даних (не входить у довжину слова). Контроль парності не використовується.

Розряди D6 та D7 визначають кількість стоп-бітів, які вводяться після біту контролю і призначені для фіксації закінчення посилання даних. Довжину стоп-біта вибираємо рівною півтора. Після запису інструкції режиму записується інструкція команди, формат якої наведений на рисунку 3.2.

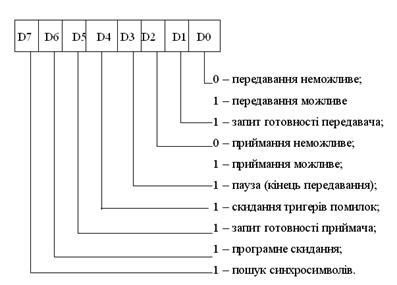

Рисунок 3.2 - Формат інструкції команд

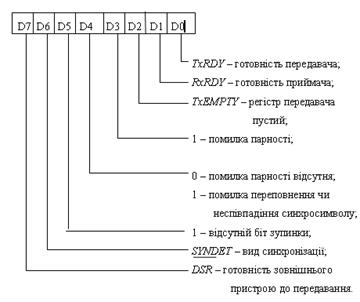

У системах передавання даних часто необхідно контролювати стан сигналів під час виконання операції. Формат регістра станів наведений на рисунку 3.3.

Рисунок 3.3 - Формат регістра стану

Біт D4 встановлюється в одиницю у випадках:

- читання наступної кодової комбінації з лінії зв’язку, коли попередня комбінація мікропроцесором зчитана не була;

- у синхронному режимі роботи із внутрішньою синхронізацією, коли попередня кодова комбінація відповідала першому синхросимволу, а наступна не відповідає другому синхросимволу;

- під час читання даних чи стану у випадку внутрішнього пересилання інформації чи синхросимволів.

Помилки не переривають роботи мікросхеми. Тригери встановлюються до початкового стану інструкцією команди. Читання стану дозволяє використовувати дану мікросхему не лише у режимі переривань, але й у режимі програмного опитування прапорів.

Прямим аналогом цієї мікросхеми є I8251 фірми Intel Corp .

3.2 Мікроконтролер КМ1816ВЕ51

З урахуванням вимог технічного завдання, для виконання пристрою міжконтролерного обміну інформацією, її кодування та декодування, а також запису інформації доцільно використати мікропроцесор КМ1816ВЕ51.

Мікроконтролер виконаний на основі високорівневої N-МОП технології і випускається в корпусі ВІС, що має 40 зовнішніх виводів. Цокольовка корпусу МК51 і найменування виводів показані на рисунку 3.4.

Для роботи МК51 потрібно одне джерело електроживлення +5 В. Через чотири порта що програмуються введення/виводу МК51 взаємодіє із середовищем у стандарті ТТЛ-схем із трьома станами виходу.