Курсовая работа: Розробка ВІС в базисі БМК 1515ХМ1 пристрою множення який множить 3-розрядне число на 2-розрядне

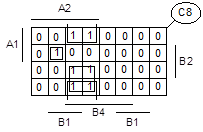

Рисунок 2.4 – Діаграма Вейча для функції С8

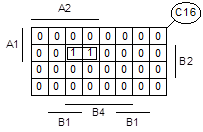

Рисунок 2.5 – Діаграма Вейча для функції С16

Відповідно до побудованих діаграм Вейча для функцій С записується їх аналітичний вигляд і приводяться до базису БМК.

![]() ;

;

![]() ;

;

![]()

![]() ;

;

![]() ;

;

![]()

Результуюча схема утворюється при реалізації даних функцій в базисі БМК1515. Схема електрична принципова наведена в додатках(Додаток Б)

3. Розрахунок швидкодії пристрою

Проектуючи принципові електричні схеми, слід приблизно оцінити середній сумарний час затримки на ланцюжку логічних елементів, не враховуючи паразитних ємностей.

Середній сумарний час затримки обчислюється за формулою:

Тсер = Т1 + Т2 + ... + Тn ,

де Ті – середній час затримки поширення сигналу на і-му елементі.

Через розкид технологічних параметрів середній час затримки поширення сигналу може відрізнятися від обчислених даних, тому треба мати запас за цим параметром[4].

Розглянемо найдовші шлях в схемі:

T1 = ![]() Z1 +

Z1 + ![]() V4V4 +

V4V4 + ![]() V1W2 + +

V1W2 + +![]() V2 +

V2 +![]() Z2 = 14,3 + 24,4 + 20 + 3,3 + 14,3 = 76,3(нс)

Z2 = 14,3 + 24,4 + 20 + 3,3 + 14,3 = 76,3(нс)

T2 = ![]() Z1 +

Z1 + ![]() V4V4 +

V4V4 + ![]() V1W3 +

V1W3 + ![]() W 8 +

W 8 + ![]() V3 +

V3 +![]() V1 +

V1 +![]() V2 +

V2 +![]() Z2 = 14,3 + 24,4 +12 + 6 + 6+3,8+3,3+14,3 = 84,1(нс)

Z2 = 14,3 + 24,4 +12 + 6 + 6+3,8+3,3+14,3 = 84,1(нс)

T3 = ![]() Z1 +

Z1 + ![]() V4V4 +

V4V4 + ![]() V1W2 +

V1W2 + ![]() V1 +

V1 + ![]() V4 +

V4 +![]() V3 +

V3 +![]() V1 +

V1 +![]() V2 +

V2 +![]() Z2 = 14,3 + 24,4 + 20 + 3,8 + 6+6+3,8+3,3+14,3 = 95,9(нс)

Z2 = 14,3 + 24,4 + 20 + 3,8 + 6+6+3,8+3,3+14,3 = 95,9(нс)

T4 = ![]() Z1 +

Z1 + ![]() V4V4 +

V4V4 + ![]() V1W 3 +

V1W 3 +![]() V1W 2 +

V1W 2 +![]() V1 +

V1 +![]() V2 +

V2 +![]() Z2 = 14,3 + 24,4 +12 + 20 +3,8+3,3+14,3 = 92,1(нс)

Z2 = 14,3 + 24,4 +12 + 20 +3,8+3,3+14,3 = 92,1(нс)

T5 = ![]() Z1 +

Z1 + ![]() V 4 V 4 +

V 4 V 4 + ![]() V3 +

V3 +![]() V2 +

V2 +![]() Z2 = 14,3 + 24,4 + 6+3,3+14,3 = 62,3(нс)

Z2 = 14,3 + 24,4 + 6+3,3+14,3 = 62,3(нс)

З розглянутих шляхів проходження сигналу найдовшим є Т3 . Отже, затримка розробленої схеми становить Т = 95,9(нс). Можна зробити висновок, що схема задовольняє поставлені вимоги.

4 . Розробка логічної моделі

Логічне моделювання цифрового виробу полягає в розробці та послідовному налагодженні логічної моделі, яка є сукупністю проектної інформації про електричну схему і конструктивних виводів у обсязі, достатньому для проектування топології й автоматичного синтезу програм контролю. Опис електронної схеми зводиться до послідовного опису структур, що її покривають. При цьому кожний функціонально-закінчений фрагмент, який повторюється, подається окремою структурою і ідентифікується своїм ім'ям. Описуючи зв'язки, кожний вивід згадується тільки один раз. Поява імені будь-якого виводу ще один раз вважається помилкою.

Виконаємо логічне моделювання даного пристрою:

Структура "Scheme"