Курсовая работа: Устройство сбора данных

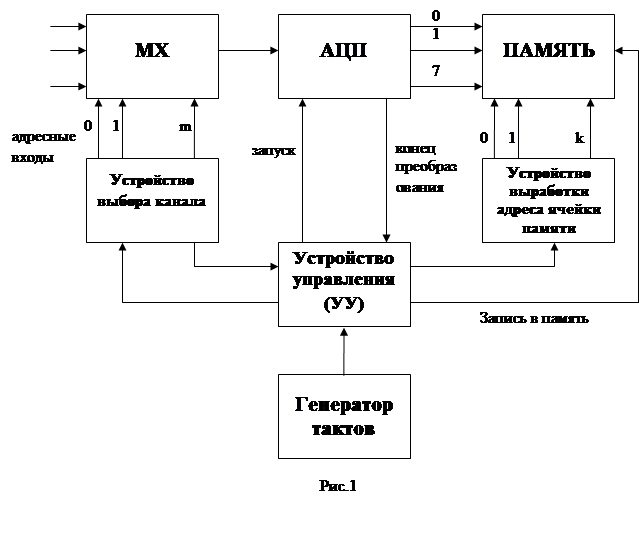

Структурная схема УСД приведена на рис. 1. В состав УСД входят:

Мультиплексор (MS): имеет F аналоговых входов и m управляющих (адресных) входов. При подаче на адресный вход двоичного числа - адреса - происходит подключение одного из аналоговых каналов, имеющих данный адрес, к выходу MS. Число опрашиваемых аналоговых каналов связано с числом адресных входов k = 2m .

АЦП: имеет 1 аналоговый вход и 8 выходов, по которым в двоичном, параллельном коде выдается число, соответствующее уровню поданного на вход АЦП отсчета аналогового сигнала. Перед началом работы АЦП на него должен быть подан сигнал запуска.

АЦП выполняет преобразования за несколько тактов. После окончания преобразования АЦП выдает сигнал ОК (окончание преобразования) на устройство управления. Сигнал ОК - флаг (обозначается как Тфл ), должен быть зафиксирован с помощью триггера до момента окончания записи данных опрашиваемого канала в ячейку памяти ОЗУ.

MS и АЦП берутся как стандартные схемы с соответствующими характеристиками.

Устройство управления на некоторых тактовых интервалах с учетом осведомительных сигналов, поступающих от других устройств (в дальнейшем такие сигналы обозначаются буквой Xi ), формирует управляющие сигналы Yn , которые обеспечивают запуск других устройств и согласованную их работу.

В ходе выполнения курсовой работы разрабатываются: ОЗУ, устройство выработки адреса памяти, устройство выработки адреса каналов, а также УУ.

|

|

Разработка блока выработки адреса ЗУ

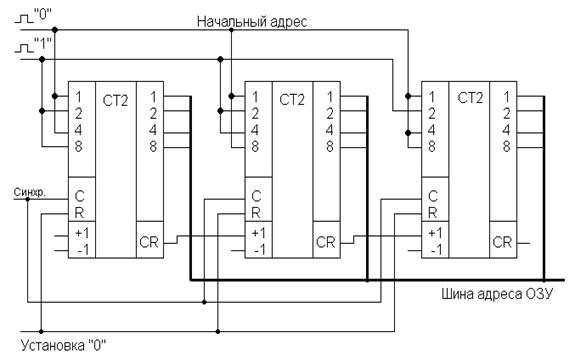

Требуется синтезировать устройство, которое могло бы, начиная с определенного начального адреса G, производить формирование последующих адресов, отличающихся друг от друга на единицу. Разработку такого устройства можно осуществить с помощью счетчиков. Длина адресного слова определяется емкостью памяти.

Емкость памяти θ = 2048 = 211

Начальный адрес ячейки памяти G = 6800 16 = 0110 1000 0000 00002

Блок будет содержать три четырехразрядных суммирующих двоичных счетчика с предустановкой. Схема блока представлена на рис. 2.

Рис. 2

Разработка блока выработки адресов каналов коммутатора

Число каналов F = 810 . Блок можно синтезировать с использованием трехразрядного двоичного счетчика, последовательно формирующего двоичные адресные числа от 1 до 4 с перекодировкой данной последовательности с помощью дешифратора (DC) и шифратора (CD). После опроса всех каналов срабатывает схема прерывания счета и формируется сигнал сброса счетчика в ноль.

Адрес опрашиваемого канала подается на коммутатор (мультиплексор) параллельным двоичным кодом через ключи. Этот делается для синхронного поступления на мультиплексор всех разрядов адресного слова.

Шифратор – устройство, осуществляющее преобразование десятичных чисел в двоичные. Для обратного преобразования двоичных чисел в небольшие по значению десятичные числа используются дешифраторы. Схема блока выработки адресов каналов коммутатора показана на рис. 3.

Рис. 3

Словесное описание цикла сбора данных

Составим словесное описание работы УСД в виде последовательности выполняемых в нем микроопераций.

1. Цикл сбора данных начинается с того, что в счетчик СТ2 блока выработки адресов ячеек памяти производится запись адреса первой ячейки области памяти ОЗУ, отведенной для хранения данных. Очевидно, что в качестве СТ2 удобно использовать такой счетчик, в котором предусмотрена возможность предустановки начального адреса (НА). Ввод начального адреса осуществляется параллельным кодом. Подав на одни входы установки НА логический ноль (потенциал земли или корпуса), а на другие - логическую единицу (напряжение источника питания), можно обеспечить запись требуемого адреса в счетчик в одном такте.

2. Счетчик СТ2 блока выработки номера канала сбрасывается в «0». Тем самым в нем формируется адрес аналогового канала, опрашиваемого первым.

3. Производится сброс в «0» триггера Тфл (гашение флага). При записи данных первого из опрашиваемого каналов Тфл = 0. Однако перед началом опроса всех последующих каналов, поскольку состояние триггеров флага фиксируется, Тфл = 1. Поэтому эта микрооперация необходима.

4. Адрес аналогового канала из СТ22 выдается на адресные входы коммутатора. Коммутатор подключает первый опрашиваемый канал к входу АЦП.

5. Производится запуск АЦП, и в нем начинается процесс аналого-цифрового преобразования.