Курсовая работа: Выполнение планирования вычислений алгоритма на однородной вычислительной сети при известной структуре

10. Вычисляем узел х, удовлетворяющий соотношению ![]() , где

, где ![]() - количество свободных связей у рассматриваемых узлов. f=1,…f `, затем полагаем i: =x, T: =T\Tк. Если

- количество свободных связей у рассматриваемых узлов. f=1,…f `, затем полагаем i: =x, T: =T\Tк. Если ![]() , то переходим к шагу 1, иначе конец алгоритма.

, то переходим к шагу 1, иначе конец алгоритма.

5. Описание интерфейса программы

Интерфейс разработанной программы состоит из одного окна, содержащих несколько вкладок:

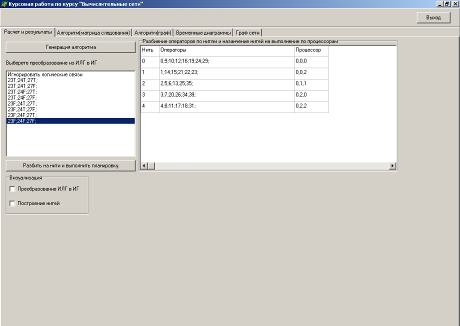

1. Вкладка генерации информационного графа алгоритма и результатов выполнения разбиения алгоритма на нити. (рис.2).

Рис.2. Вкладка управления работой программы

На вкладке можно осуществить генерацию ИЛГ, выбрать метод преобразования ИЛГ в ИГ и задать режим визуализации (какие построения необходимо визуализировать).

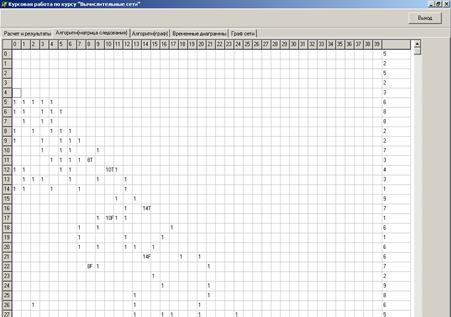

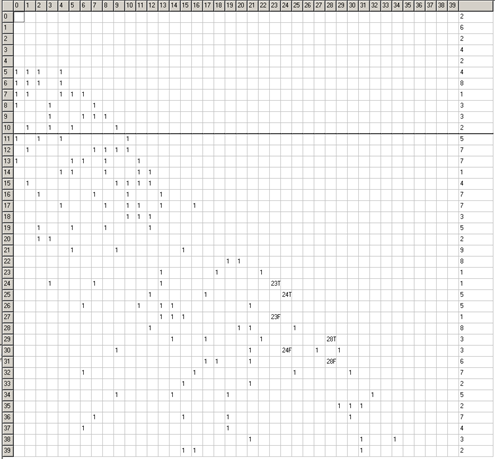

2. Вкладка вывода информационного графа, заданного матрицей следования (рис.3).

Содержит сгенерированную матрицу следования алгоритма. В крайнем правом столбце приведены веса операторов, веса связей не приводятся, что бы можно было легче анализировать матрицу визуально.

В матрице следования в столбцах задаются все выходящие из данной вершины связи, а в строках - все входящие в заданную вершину связи. При этом задаваемое значение 1 означает, что связь между операторами есть, если связь пронумерована с буквами ‘T’ или ‘F’, то это соответствующая логическая связь. Если связи между вершинами нет, то позиция не заполняется.

Поскольку ИЛГ по заданию не должен содержать циклов, то данные можно вводить только ниже главной диагонали матрицы следования.

Рис.3 - Окно вывода информационного графа.

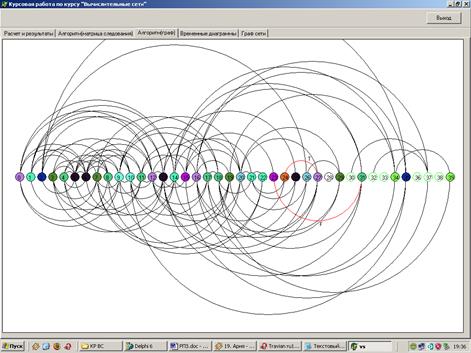

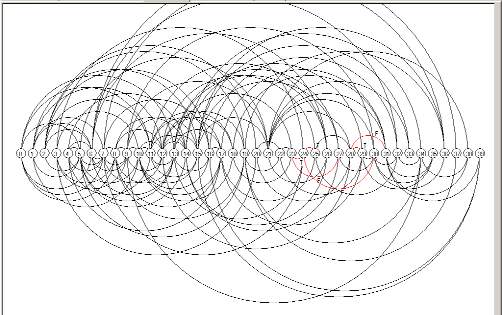

3. Окно вывода информационного графа, заданного матрицей следования (рис.4).

Отображает алгоритм в виде графа, что упрощает визуальный анализ. При настройке параметров визуализации показывает процесс построения нитей и преобразования ИЛГ в ИГ.

Рис.4 - Вкладка вывода ИЛГ.

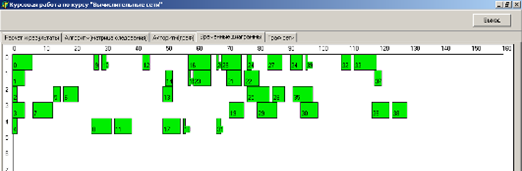

4. Временные диаграммы распределения нитей по процессорам (рис.4).

Здесь указывается, какой нити принадлежит оператор, и в какие сроки он выполняется.

Рис.4. Временные диаграммы нитей.

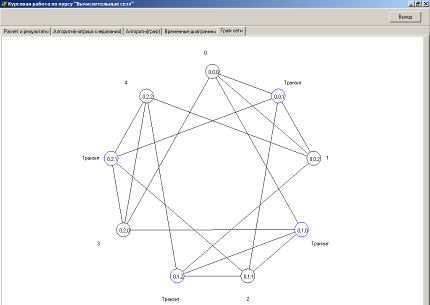

5. Вкладка распределения нитей по процессорам. Содержит описание структуры ВС с указанием, какой процессор выполняет какую нить, какой является транзитным и какой свободен. (рис.5)

Рис.5. Окно вывода результатов

6. Результаты работы программы

На рисунке 6 показана сгенерированная матрица следования S.

Рис.6. Сгенерированная матрица следования S

На рисунке 7 показан построенный программой по указанной в задании матрице S ИЛГ задачи.

Рис.7. ИЛГ задачи.