Реферат: Аналого-цифровой преобразователь АЦП

Блок делителей опорного напряжения представляет собой линейку резисторов с отношением сопротивленя следующего резистора к предыдущему как 2/1, т.е. сопротивление резистора R1(см. Рис. 7) равно сумме всех следующих резисторов - R1=R2+R3+R4+R5+R6; сопротивление резистора R2=R3+R4+R5+R6 и т.д. Соответственно напряжение в точке "a" будет равно половине опорного напряжения, в точке "b" - четверти и т.д.

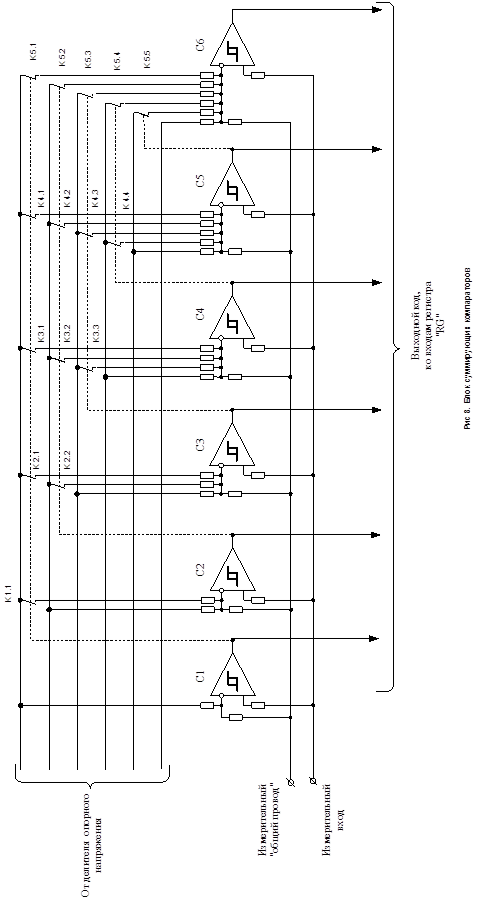

2.5. Блок суммирующих компараторов с аналоговыми ключами для "взвешенного сигнала".

Блок компараторов с аналоговыми ключами является ядром АЦП, именно он производит преобразование аналогового сигнала в цифровой код.(Рис 8)

Преобразогвание аналогового сигнала в цифровой происходит непрерывно, т.е. любое изменение входного сигнала, за исключением временных задержек схемы, тотчас преобразуется в цифровой код.

Схема работает следующим образом.

АПЗ.38.098424.003 ПЗ

Лист

14

Изм

Лит

№ докум

Подпись

Дата

| |||||||||

АПЗ.38.098424.003 ПЗ | Лист | ||||||||

| 15 | |||||||||

| Изм | Лит | № докум | Подпись | Дата | |||||

Входной сигнал подаётся одновременно на входы всех компараторов. Компаратор C1 сравнивает входной сигнал с половиной опорного напряжения, если входной сигнал превышает половину опорного напряжения то на выходе компаратора появляется высокий уровень, который вызывает включение аналоговых ключей Kx.1, и следовательно подачу Uоп/2 на входы остальных компараторов, также этот высокий уровень поступает на вход D1 регистра "RG". Компаратор C2 сравнивает входной сигнал с одной четвёртой опорного напряжения, если входной сигнал не превышает половины опорного напряжения, если превышает то сравнивает с суммой 1/4 и 1/2 опорного напряжения. В любом из случаев если входной сигнал превышает опорный(сумму опорных) компаратор C2 включает Uоп/4 на входы последующих компараторов подаёт "1" на вход D2 регистра "RG", в противном случае Uоп/4 не подаётся к последующим компараторам и на входе D2 регистра "RG" "0". Аналогичным образом работают последующие каскады. Вследствии того, что цифровой код на выходе преобразователя непрерывно изменяется, отслеживая входной сигнал, то необходимая частота дискретизации задаётся программно, с учётом временных задержек элементов схемы. | |||||||||

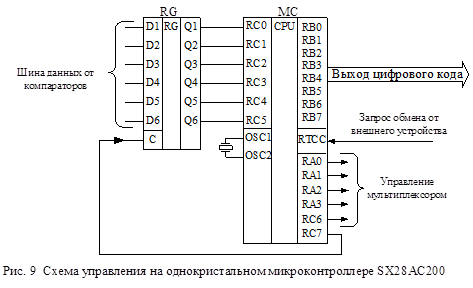

| 2.6. Схема управления на микроконтроллере. Схема управления на микроконтроллере состоит из регистра "RG" 74AC373 или любого функционально аналогичного и однокристального микроконтроллера "MC" типа SX28AC200 производства фирмы "SCENIX" с тактовой частотой 200МГц(см. Рис. 9). | |||||||||

АПЗ.38.098424.003 ПЗ | Лист | ||||||||

| 17 | |||||||||

| Изм | Лит | № докум | Подпись | Дата | |||||

|

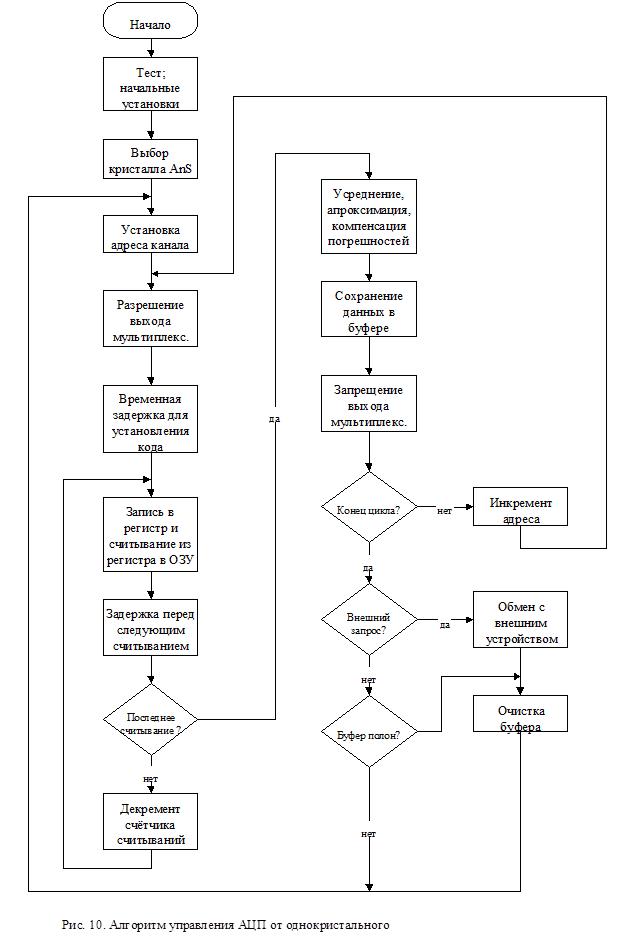

Микроконтроллер после запуска по завершении программы теста и начальных установок (см. алгоритм на рис. 10 ) выбирает мультиплексор AnS вход CE-, выставляет на входах A0-A2 адрес канала I0 и сигналом OE- разрешает передачу входного сигнала I0 на выход OUT мультиплексора, по истечении выдержки времени неоходимой для установления кода на входах регистра "RG" микроконтроллер даёт команду записи в регистр, из которого считывает данные во внутренее ОЗУ, после чего следуют програмно-заданное кличество циклов выдержки времени, записи в регистр и переноса в ОЗУ. Далее сигналом OE- запрещается передача со входа I0 на выход мультиплексора, устанавливается на входах A0-A2 адрес следующего канала и производится цикл преобразования и считывания. По окончании цикла поледнего считывания канала микроконтроллер производит завершение операций по обработке полученых значений и сохраняет данные в буфере. Далее запрещается передача входного аналогового сигнала на выход мультиплексора и если считан не последний канал, то инкрементируется адрес канала мультиплексора и продолжается цикл чтения и преобразования. По завершении цикла обработки последнего канала проверяется был ли запрос на обмен от внешнего устройства, если да то производится обмен и очищается буфер, иначе буфер проверяется на переполнение и при необходимости очищается, после чего весь цикл повторяется. | |||||||||

АПЗ.38.098424.010 П3 | Лист | ||||||||

| 19 | |||||||||

| Изм | Лит | № докум | Подпись | Дата | |||||

|

| |||||||||

АПЗ.38.098424.003 ПЗ | Лист | ||||||||

| 20 | |||||||||

| Изм | Лит | № докум | Подпись | Дата | |||||

| 5. Расчет временных характеристик. Быстродействие схемы определяется временными задержками элементов схемы, и расчитывается как сумма всех послеловательно включенных элементов в наименее быстродействующей ветви схемы, умноженной на коэффициент 1.15, т.е. если обработка сигнала производится параллельно несколькими участками схемы то за основу для расчётов берётся участок имеющий наибольшее время задержки. В данном случае обработка сигнала идёт по одной ветви и следовательно задержка равна: tALL =1.15*(tMX +tA1 +6*tCMP +5*tSW +tCM1 +tB +tK_SPP ), где tMX - время задержки входного мультиплексора nS; tA1 - время задержки входного усилителя nS; tCMP - время задержки одного компаратора преобразователя nS; 5tSW - время задержки одного аналогового ключа преобразователя nS; tCM1 - время задержки компаратора переключателя полярности nS; tB - время задержки буферных элементов переключателя полярности nS; tK_SPP - время задержки одного аналогового ключа переключателя полярности nS. | |||||||||

АПЗ.38.098424.003 ПЗ | Лист | ||||||||

| 22 | |||||||||

| Изм | Лит |

№ докум |

Подпись |

Дата | |||||

|

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ 1. П.Хоровиц, У. Хилл Искуство схемотехники 1 том. Москва «Мир» 1993. 2. П.Хоровиц, У. Хилл Искуство схемотехники 2 том. Москва «Мир» 1993. 3. П.Хоровиц, У. Хилл Искуство схемотехники 3 том. Москва «Мир» 1993. 4. Богданович М.И., Грель И.Н. “Цифровые интегральные микросхемы”. Минск “Беларусь”, 1991. 5. Гутников В.С. Интегральная электроника в измерительных устройствах. Энергоатом издат 1988 К-во Просмотров: 1087

Бесплатно скачать Реферат: Аналого-цифровой преобразователь АЦП

| |||||||||

3. Алгоритм управления АЦП.

3. Алгоритм управления АЦП.