Реферат: Архітектура Virtex

На вхід мультиплексора F5 подаються сигнали з виходів функціональних генераторів даної секції КЛБ. Цей вузол може працювати як функціональний генератор, що реалізовує будь-яку 5-входовую функцію, або як мультиплексор 4:1, або як деяка функція від дев'яти вхідних змінних.

Аналогічно, мультиплексор F6 об'єднує виходи всіх чотирьох функціональних генераторів КЛБ, використовуючи один з виходів мультиплексора F5. Це дозволяє реалізувати або будь-яку 6-входовую функцію, або мультиплексор 8:1, або деяку функцію до 19 змінних.

Кожен КЛБ має чотири крізні лінії – по одній на кожен логічний комірка. Ці лінії використовуються як додаткові входи даних, або як додаткові ресурси трасувань, що не витрачають логічні ресурси.

Арифметична логіка

Кожна ЛЯ містить спеціальну логіку прискореного перенесення, яка забезпечує якнайкращу реалізацію на ПЛІС різних арифметичних функцій. КЛБ містить два окремі ланцюги перенесення – по одній на кожну секцію. Розмірність ланцюга перенесення – два біти на КЛБ.

Арифметична логіка включає елемент, що реалізовує функцію виключає АБО, який дозволяє реалізувати однобітовий суматор в одному логічному комірці.

У кожному логічному комірці є елемент, що реалізовує функцію І (AND), який призначений для побудови швидкодійних помножувачів.

Спеціальні траси логіки прискореного перенесення можуть також використовуватися для каскадного включення функціональних генераторів при необхідності створення функцій з великою кількістю вхідних змінних.

Буфери з трьома станами

Кожен КЛБ Virtex містить два буфери з трьома станами, які навантажені на внутрішні шини. Кожен буфер BUFT має незалежний вхід управління з третім станом і незалежний вхідний контакт.

Блокова пам'ять ( Block RAM )

У FPGA Virtex вбудована особлива блокова пам'ять (Block Select RAM) великої ємністі. Вона створена на додаток до розподіленої пам'яті невеликої ємністі (Select RAM), реалізованої на таблицях перетворення (Look Up Table RAM – LUTRAM).

Блоки пам'яті Block Select RAM+ організовані у вигляді стовпців. Всі пристрої Virtex містять два такі стовпці, поодинці уздовж кожної вертикальної сторони кристала. Ці колонки збільшують повний розмір кристала. Кожен блок пам'яті рівний по висоті чотирьом КЛБ, таким чином, мікросхема Virtex, що має 64 КЛБ по висоті, містить 1–6 блоків пам'яті на колонку і 32 блоки пам'яті в цілому. У Табл. 2 приводяться ємністі блокової пам'яті для різних кристалів Virtex.

Таблиця 2. – Ємність блокової пам'яті

| Кристал Virtex | Число блоків | Загальний об'єм блокової пам'яті [битий] |

| XCV50 | 8 | 32 768 |

| XCV100 | 10 | 40 960 |

| XCV150 | 12 | 49 152 |

| XCV200 | 14 | 57 344 |

| XCV300 | 16 | 65 536 |

| XCV400 | 20 | 81 920 |

| XCV600 | 24 | 98 304 |

| XCV800 | 28 | 114 688 |

| XCV1000 | 32 | 131 072 |

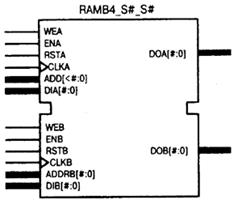

Кожен блок пам'яті, це повністю синхронне двохпортове ОЗУ з незалежним управлінням для кожного порту. Розмірність шини даних для обох портів може бути конфігурована незалежно, що дозволяє створювати перетворювачі розмірності шини. У Табл. 2 показані можливі співвідношення размерностей шин даних і адреси.

У кристалах Virtex створені спеціальні ресурси трасувань для зв'язку блокової пам'яті з блоками КЛБ і іншими блоками пам'яті.

Рисунок 4. – Блок пам’яті

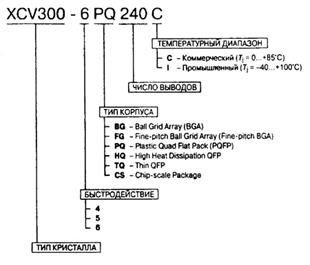

5. Позначення мікросхем сімейства Virtex

Спосіб позначення мікросхем сімейства Virtex показаний на рисунку 5.

Рисунок 5 – Визначення МС сімейства Virtex

ПЛІС доцільно застосовувати при розробці оригінальної апаратури, а також для заміни звичайних ІС малому і середньому ступеню інтеграції. При цьому значно зменшуються розміри пристрою, знижується споживана потужність і підвищується надійність.

Найбільш ефективне використовування ПЛІС у виробах, що вимагають нестандартних рішень схемотехніки. У цих випадках ПЛІС навіть середнього ступеня інтеграції (24 виводи) замінює, як правило, до 10–15 звичайних інтегральних мікросхем.

Іншим критерієм використовування ПЛІС є потреба різко скоротити терміни і витрати на проектування, а також підвищити Спроможність модифікації і наладки апаратури. Тому ПЛІС широко застосовується в стендовому устаткуванні, на етапах розробки і виробництва досвідченої партії нових виробів, а також для емуляції схем, що підлягають подальшій реалізації на іншій елементній базі, зокрема БМК.

Окрема область застосування ПЛІС – проектування на їх основі пристроїв для захисту програмного забезпечення і апаратури від несанкціонованого доступу і копіювання. ПЛІС володіють такою технологічною особливістю, як «біт секретності», після програмування якого схема стає недоступною для читання (хоча свої функції ПЛІС, природно, продовжує виконувати). Звичайно застосування однієї-двох ПЛІС середнього ступеня інтеграції виявляється цілком достатньою для надійного захисту інформації.

Найбільш ширше програмовані логічні ІС використовуються в мікропроцесорній і обчислювальній техніці. На їх основі розробляються контролери, адресні дешифратори, логіка обрамлення мікропроцесорів, формувачі управляючих сигналів і ін. На ПЛІС часто виготовляють мікро програмні автомати і інші спеціалізовані пристрої, наприклад, цифрові фільтри, схеми обробки сигналів і зображення, процесори швидкого перетворення функцій Фурье і т.д. У техніці зв'язку

ПЛІС застосовуються в апаратурі ущільнення телефонних сигналів.

Застосування ПЛІС стає актуальним ще і тому, що у розробників часто немає необхідних стандартних мікросхем.