Реферат: Архітектура Virtex

1. Банки вводу-виводу

Деякі з описаних вище стандартів вимагають підключення напруги ![]() чи

чи ![]() . Ці зовнішні напруги підключаються до контактів мікросхеми, які функціонують групами, названими банками.

. Ці зовнішні напруги підключаються до контактів мікросхеми, які функціонують групами, названими банками.

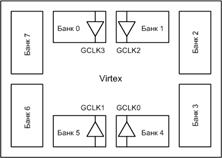

Кожна сторона кристала мікросхеми розділена на два банки. Кожен банк має декілька контактів ![]() , але всі вони повинні бути підключені до однієї і тієї ж напруги. Ця напруга визначається вибраною для даного банка стандартом вихідних сигналів.

, але всі вони повинні бути підключені до однієї і тієї ж напруги. Ця напруга визначається вибраною для даного банка стандартом вихідних сигналів.

Стандарти для вихідних сигналів конкретного банку можуть бути різними лише в тому випадку, якщо вони використовують однакове значення напруги ![]() . Сумісні стандарти показані в Табл. 1. GTL і GTL+ присутні скрізь, оскільки їх виходи з відкритим стоком не залежать від значення

. Сумісні стандарти показані в Табл. 1. GTL і GTL+ присутні скрізь, оскільки їх виходи з відкритим стоком не залежать від значення ![]() .

.

Рисунок 1. – Банки вводу-виводу Virtex

Деякі сигнальні стандарти вимагають подачі відповідних порогових напруг ![]() на вхідні каскади. При цьому визначені БВВ автоматично конфігуруються як входи, відповідні напрузі

на вхідні каскади. При цьому визначені БВВ автоматично конфігуруються як входи, відповідні напрузі ![]() . Приблизно один контакт з шести в кожному банку може виконувати цю роль.

. Приблизно один контакт з шести в кожному банку може виконувати цю роль.

Таблиця 1. Вихідні сумісні стандарти

| Сумісні стандарти | |

| 3.3 У | PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL+ |

| 2.5 У | SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+ |

| 1.5 У | HSTL I, HSTL III, HSTL IV, GTL, GTL+ |

Контакти ![]() в межах одного банку внутрішньо між собою сполучені, отже, лише одне значення напруги

в межах одного банку внутрішньо між собою сполучені, отже, лише одне значення напруги ![]() може бути використано в рамках одного банку. Для правильної роботи всі контакти

може бути використано в рамках одного банку. Для правильної роботи всі контакти ![]() одного банку повинні бути приєднані до зовнішнього джерела напруги.

одного банку повинні бути приєднані до зовнішнього джерела напруги.

В межах одного банку можна одночасно використовувати входи, які вимагають напруги ![]() і входи, які цього не вимагають. В той же час, лише одне значення напруги

і входи, які цього не вимагають. В той же час, лише одне значення напруги ![]() може бути використано в рамках одного банку. Вхідні буфери, які використовують

може бути використано в рамках одного банку. Вхідні буфери, які використовують ![]() , не сумісні з сигналами 5-в стандартів.

, не сумісні з сигналами 5-в стандартів.

Контакти ![]() і

і ![]() для кожного банку приведені в таблицях і діаграмах під конкретний корпус і кристал. На діаграмах також показано, до якого банку відноситься конкретний контакт введення-висновку.

для кожного банку приведені в таблицях і діаграмах під конкретний корпус і кристал. На діаграмах також показано, до якого банку відноситься конкретний контакт введення-висновку.

В рамках конкретного типу корпусу мікросхеми число контактів ![]() і

і ![]() може мінятися залежно від ємністі кристала. Чим більше кристал по логічній ємністі, тим більше число контактів введення-висновку перетворене в контакти типу

може мінятися залежно від ємністі кристала. Чим більше кристал по логічній ємністі, тим більше число контактів введення-висновку перетворене в контакти типу ![]() . Оскільки існує максимальний набір контактів

. Оскільки існує максимальний набір контактів ![]() для менших кристалів, є Спроможність проектування друкарської платні, що дозволяє також використовувати на ній і великі кристали з таким же типом корпусу. Всі контакти

для менших кристалів, є Спроможність проектування друкарської платні, що дозволяє також використовувати на ній і великі кристали з таким же типом корпусу. Всі контакти ![]() , передбачувані до використовування для великих кристалів, при цьому повинні бути приєднані до напруги

, передбачувані до використовування для великих кристалів, при цьому повинні бути приєднані до напруги ![]() і не повинні використовуватися як контакти введення-висновку.

і не повинні використовуватися як контакти введення-висновку.

У менших кристалах деякі з контактів ![]() , використовувані у великих кристалах, не сполучені усередині корпусу. Ці не приєднані контакти можуть бути залишені не приєднаними поза мікросхемою або бути підключені до напруги

, використовувані у великих кристалах, не сполучені усередині корпусу. Ці не приєднані контакти можуть бути залишені не приєднаними поза мікросхемою або бути підключені до напруги ![]() при необхідності забезпечення сумісності друкарської платні, що розробляється, з великими кристалами.

при необхідності забезпечення сумісності друкарської платні, що розробляється, з великими кристалами.

У корпусах типа TQ-144 і PQ-240/HQ-240 всі контакти ![]() сполучені разом усередині мікросхеми і, отже, до всіх з них повинна бути підключене одна і та ж напруга

сполучені разом усередині мікросхеми і, отже, до всіх з них повинна бути підключене одна і та ж напруга ![]() . У корпусі CS-144 пари банків, розташовані на одній стороні, внутрішньо сполучені, забезпечуючи, таким чином, Спроможність вибору лише чотирьох можливих значень напруги для

. У корпусі CS-144 пари банків, розташовані на одній стороні, внутрішньо сполучені, забезпечуючи, таким чином, Спроможність вибору лише чотирьох можливих значень напруги для ![]() . Контакти

. Контакти ![]() залишаються внутрішньо сполученими в рамках кожного з восьми банків і можуть використовуватися, як було описано вище.

залишаються внутрішньо сполученими в рамках кожного з восьми банків і можуть використовуватися, як було описано вище.

2. Логічний блок, що конфігурується – КЛБ

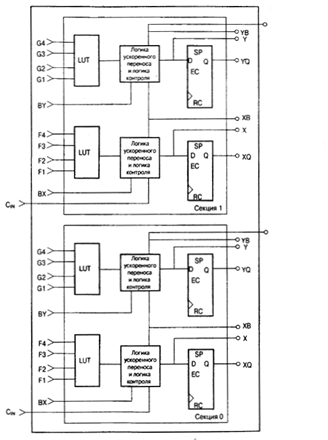

Базовим елементом КЛБ є логічний комірка – ЛЯ (Logic Cell – LC). ЛЯ складається з 4-входового функціонального генератора, логіки прискореного перенесення і елементу, що запам'ятовує. Вихід кожного функціонального генератора кожного логічного комірці приєднаний до виходу КЛБ і до D-входу тригера. Кожен КЛБ серії Virtex містить чотири логічні комірки, організовані у вигляді двох однакових секцій.

Рисунок 2. – Секційний КЛБ Virtex

На додаток до чотирьох базових логічних комірок, КЛБ серії Virtex містить логіку, яка дозволяє комбінувати ресурси функціональних генераторів для реалізації функцій від п'яти або шести змінних. Таким чином, при оцінці числа еквівалентних системних вентилів для мікросхем сімейства Virtex, кожен КЛБ прирівнюється до 4.5 ЛЯ.

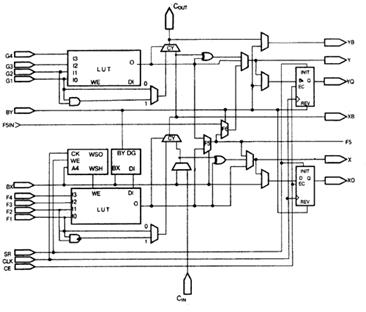

Рисунок 3. – Детальний вид секції Virtex

3. Таблиця перетворення

Функціональні генератори реалізовані у вигляді 4-входових таблиць перетворення (Look-Up Table – LUT). Окрім використовування як функціональні генератори, кожен LUT-елемент може бути також використаний як синхронне ОЗУ розмірністю 16х1 біт. Більш того, з двох LUT-елементів в рамках однієї секції можна реалізувати синхронне ОЗУ розмірністю 16х2 біта або 32х1 біт, або двохпортове синхронне ОЗУ розмірністю 16х1 біт.

На LUT-елементі мікросхеми Virtex може бути реалізований 16-розрядний сдвиговий регістр, який ідеально підходить для захоплення високошвидкісних або пакетних потоків даних. Цей режим може також використовуватися для запам'ятовування даних в додатках цифрової обробки сигналів.

4. Елементи, що запам'ятовують

Елементи, що запам'ятовують, в кожній секції КЛБ Virtex можуть конфігуруватися як динамічні тригери (чутливі до фронту сигналу) D-типу, або як тригери – клямки, чутливі до рівня сигналу. D-вхід тригера може управлятися або від функціонального генератора в рамках тієї ж секції КЛБ, або безпосередньо від входів даної секції КЛБ, минувши функціональні генератори.

Окрім сигналів синхронізації (Clock) і дозволи синхронізації (Clock Enable – ЦЕ) в кожній секції КЛБ є сигнали синхронної установки (Set) і скидання (Reset). Позначення цих сигналів – SR і BY відповідно.

Сигнал SR переводить елемент, що запам'ятовує, в стан, визначений для нього в конфігураційних даних, а сигнал BY – в протилежний стан. Ці ж сигнали можуть бути використані також як асинхронна передустановка (Preset) і очищення (Clear). Всі сигнали управління можуть бути незалежно проінвертіровани. Вони подаються на обидва тригери в рамках конкретної секції КЛБ.

Додаткова логіка

--> ЧИТАТЬ ПОЛНОСТЬЮ <--