Реферат: Десятично-двоичный сумматор

В настоящее время интегральные микросхемы (ИМС) широко применяются в радиоэлектронной аппаратуре, в вычислительных устройствах, устройствах автоматики и т.д. Цифровые методы и цифровые устройства, реализованные на интегральных микросхемах разной степени интеграции, в том числе на микропроцессорных средствах, имеют широкие перспективы использования в цифровых системах передачи и распределения информации, в телевизионной, радиовещательной и другой аппаратуре связи. Современный этап развития научно – технического процесса характеризуется широкими применением электроники и микроэлектроники во всех сферах жизнедеятельности человека. Важную при этом сыграло появление и быстрое совершенствование ИМС – основной элементной базы современной электроники. С внедрением ИМС значительно снизилась себестоимость радиоэлектронных приборов, они стали более доступными и более компактными и расширилось внедрение радиоэлектроники в развитие науки и техники.

В отличии от цифровых устройств некоторые импульсные устройства, например формирователи и генераторы импульсов различной формы производить серийно в виде интегральных схем (ИС) экономически невыгодно. Перспективен другой путь – построение импульсных устройств на ИС широкого применения т.е на логических элементах, операционных усилителях и других ИС совместно с навесными элементами. Это способствует унификации элементной базы, эффетивному использованию и комплексной миниатюризации радиоэлектронной аппаратуры – высокая надёжность, малые габариты и масса, низкая стоимость и потребляемая мощность.

1. Общая часть.

1.1. Назначение арифметически - логических интегральных схем.

Арифметически – логические интегральные микросхемы, являются неотъемлемой частью микроэлектронных цифровых вычислительных устройств и предназначены для выполнения арифметических и логических операций над числами, представленными в двоичном, двоично – десятичном и других кодах. Для выполнения арифметических операций АЛУ строят на сумматорах.

Сумматором называется устройство, выполняющее арифметическое сложение двух чисел, представленных сигналами на его входах. При необходимости сумматоры с помощью некоторых вспомогательных операций (сдвига числа, обращения кода числа) могут выполнять алгебраическое сложение, вычитание, умножение, деление, сравнение и другие действия с числами.

1.2. Классификация сумматоров .

Сумматоры классифицируются по следующим признакам.

По основанию системы исчисления чисел, с которыми оперирует сумматор ( двоичные, двоично –десятичные и другие ) .

По способу обработки многоразрядных чисел. Передача числа из одного места ЭЦВМ в другое может выполнятся последовательно или параллельно. В устройствах последовательного действия цифры какого – либо числа, начиная с младшего разряда, последовательно передаются в канал, обладающий емкостью в одну цифру. В устройствах параллельного действия все цифры числа передаются одновременно, поэтому емкость канала должна быть N цифр. В таком устройстве передача всего числа осуществляется за такое же время как у последовательного одна цифра. Суммирование может так же осуществляться последовательно – параллельно и параллельно – последовательно.

По способу организации цепей переноса.

По способу организации процесса суммирования одноразрядной суммирующей схемы ( комбинационный или накапливающий типы ).

1.3. Выбор и обоснование функциональной схемы .

Последовательно – параллельный тип сумматора. ( Смотри рисунок 1)

Количество одноразрядных суммирующих схем в таком сумматоре меньше количества разрядов в суммируемых числах. Эти схемы соединены между собой в цепочку в порядке последовательного возрастания разрядов. На входы сумматора поступает группа цифр младших разрядов слагаемых, причем перенос образующийся на входе старшей одноразрядной суммирующей схемы, запоминается соответствующим устройством. Затем на входы сумматора поступает следующая группа слагаемых. Одновременно на соответствующий вход младшей одноразрядной суммирующей схемы поступает перенос, который хранится в запоминающей схеме.

Элементная база .

В качестве элементной базы для построения арифметического устройства использованы ИМС серии К155ТМ2, К155ИР1, К155ИМ1.

К155ТМ2.

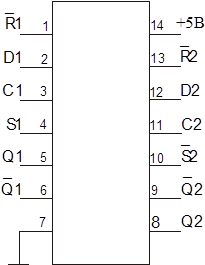

ИМС серии К155ТМ2 (рис1) содержат два независимых D-триггера имеющих общую цепь питания

У каждого триггера есть входы D, S и R, а так же комплиментарные выходы Q и Q. Входы R и S – асинхронные, потому что они работают независимо от сигнала на тактовом входе. Напряжение питания +5В подаётся на контакт 14, а питание 0В на контакт 7.

Параметры и эксплуатационные данные ИМС К155ТМ2 приведены в таблице 1.

--> ЧИТАТЬ ПОЛНОСТЬЮ <--