Реферат: Интегральная микросхема КР1533ТВ6

где Yi= 0 или 1 - состояние 1-го триггера (i = 1 - 4, начиная со входа счетчика); Рj= 2^i - 1 - вес i-го разряда счетчика. О таких счетчиках

|

говорят, что они работают в весовом коде 1-2-4-8. Счетчик может быть построен так, что его весовой код будет отличаться от рассмотренного. Так, для четырехразрядных счетчиков получили распространение коды 1-2-4-6, 1-2-2-4 и др. Существуют такие структуры счетчиков, состояние которых не может быть выражено приведенной выше формулой. О таких счетчиках говорят, что они работают в невесовом коде. Их состояния определяют по временным диаграммам или таблицам переходов. Сказанное о четырехразрядных счетчиках распространяется на счетчики любой разрядности. Делители частоты (далее просто делители) отличаются от счетчиков тем, что в них используется только один выход - выход последнего триггера. Таким образом, n-разрядный двоичный счетчик всегда можно рассматривать как делитель на 2^n. Часто необходимо осуществить деление частоты на некоторое целое число т, не являющееся степенью двойки, в таких случаях обычно используют n-разрядный двоичный счетчик (2^n >m) и вводом дополнительных логических связей обеспечивают пропуск 2^n - m состояний в процессе счета. Этого можно достигнуть, например, принудительной установкой счетчика в 0 при достижении состояния m или принудительной установкой счетчика в состояние 2^n - m при его переполнении. Возможны и другие способы. Например, наиболее часто применяемая декада (счетчик с коэффициентом пересчета 10) нa JK-триггерах К155ТВ1 строится по схеме рис. 18 (а). При подаче импульсов с 1-го по 8-й декада работает как обычный двоичный счетчик импульсов. К моменту подачи восьмого импульса на двух входах J четвертого

триггера формируется уровень лог. 1, восьмым импульсом этот триггер переключается в единичное состояние и уровень лог. 0 с его инверсного |

|

выхода, подаваемый на вход J второго триггера, запрещает его переключение в единичное состояние под действием десятого импульса. Десятый импульс восстанавливает нулевое состояние четвертого триггера, и цикл работы делителя повторяется. Декада на рис. 18 (а) работает в весовом коде 1-2-4-8. Временная диаграмма ее работы приведена на рис. 18 (б). Декада на D-триггерах, схема которой приведена на рис. 19 (а), работает в невесовом коде. Временная диаграмма ее работы приведена на рис. 19 (б).

Построение счетчиков с коэффициентом пересчета 10 (декад) на триггерах ТВ6, ТВ9, ТВ10 отличается от построения на триггерах К155ТВ1, так как у триггеров указанных микросхем по одному входу J и К. На рис. 20 приведена схема декады, работающей в весовом коде 1-2-4-8. Для увеличения числа входов J до необходимого использован один элемент микросхемы К555ЛИ1. На рис. 21 (а) приведена схема декады, выходной код которой не является весовым. Работа декады проиллюстрирована на диаграмме рис. 21 (б). Элемент DD3 не является обязательным, он преобразует код работы декады в весовой код 1-2-4-8 (выходы А, В, С, Е), что может быть необходимым для подключения к декаде дешифратора или преобразователя кода для семисегментного индикатора. |

|

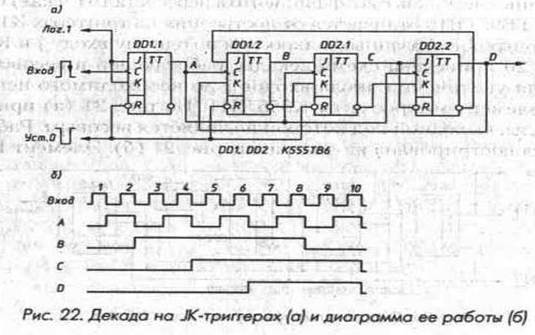

Декада, схема которой приведена на рис. 22 (а), также работает в невесовом коде. Делитель на пять DD1.2, DD2.1, DD2.2 этой декады выполнен на основе сдвигающего регистра с перекрестными связями так же, как и декады на D-триггерах рис. 19 (а). Коэффициент деления шесть такого регистра уменьшен до пяти за счет подключения входа R триггера DD2.2 к прямому выходу триггера DD2.1. Временная диаграмма работы приведена на рис. 22 (б). |

|

Микросхема ТР2 (см. рис. 16) - четыре RS-триггера. Два триггера микросхемы имеют по одному входу R и S, два других - по одному входу R и по два входа S. Сброс и установка триггеров в 1 происходят при подаче лог. 0 соответственно на входы R и S. Входы S тех триггеров, гдеих два, собраны как логический элемент ИЛИ для сигналов лог. 0, поэтому для установки триггеров в состояние 1 достаточно подать лог. 0 на один из входов S, состояние второго при этом не играет роли. Если на входы R и S триггера подать лог. 0, на выходе триггера - лог. 1. Состояние триггера после снятия сигналов лог. 0 со входов R и S будет определяться тем, с какого из входов лог. 0 будет снят последним. Микросхему ТР2 можно использовать для подавления дребезга контактов (рис. 23) и в других случаях. |

| 3. Описание схемы Микросхема КР1533ТВ6 представляет собой два JK-триггера, срабатывающих по отрицательному фронту тактового сигнала, со входами сброса. Низкий уровень напряжения на входе сброса R устанавливает прямой выход Q соответствующего триггера в состояние низкого уровня напряжения вне зависимости от логического состояния на других входах.

При наличии на входе сброса напряжения высокого уровня для правильной работы триггера требуется предварительная установка информации по входам J и К относительно отрицательного фронта тактового сигнала, а также

Маломощные быстродействующие цифровые ИМС серии КР1533 предназначены для организации высокоскоростного обмена и обработки цифровой информации, временного и электрического согласования сигналов в вычислительных системах. Микросхемы по сравнению с известными сериями логических ТТЛ микросхем обладают минимальным значением произведения быстродействия на рассеиваемую мощность. Аналог- серия SN74ALS фирмы Texas Instruments. Микросхемы изготавливаются по усовершенствованной эпитоксиально – планарной технологии с диодами Шоттки и окисной изоляцией, одно- и двухуровневой металлизированной разводкой на основе PtSi-TiW0AlSi. Конструктивно микросхемы серии КР1533 выполнены в 14-, 16-, 20-, и 24- выводных стандартных пластмассовых корпусах типа 201, 14-1, 238.16-1, 2140.20-8, 2142.42-2. Технические характеристики : Стандартные ТТЛ входные и выходные уровни сигналов. Напряжение питания 5,0 В ±10%. Задержка на вентиль 4 нс. Мощность потребления на вентиль 1мВт. К-во Просмотров: 1200

Бесплатно скачать Реферат: Интегральная микросхема КР1533ТВ6

|