Реферат: Логические элементы интегральных микросхем

Базовые элементы И-НЕ для двух указанных групп DTL-ИМС приведены на рис. 4, а, б соответственно.

Применение усилителя на составном транзисторе позволяет снизить требования к коэффициенту усиления интегральных транзисторов, а также расширить температурный диапазон работы DTL-ИМС.

Модифицированные DTL-ИМС со свободным коллектором позволяют простым способом реализовать двухступенчатую логическую функцию И-ИЛИ-НЕ за счет объединения коллекторов выходных транзисторов.

Общим свойством описанных микросхем является использование нелинейного режима работы активных элементов. Усилители логических схем характеризуются надежным запиранием транзисторов в одном логическом состоянии и насыщением транзисторов в другом.

Режим насыщения не позволяет полностью использовать высокие частотные свойства транзисторов в микросхеме, так как основная задержка определяется длительным рассасыванием заряда при включении насыщенного транзистора.

В связи с разработкой новых поколений ЭВМ встал вопрос о создании ИМС с быстродействием более 50 МГц. Этим требованиям удовлетворяют ИМС с эмиттерными связями (ECL-ИМС), имеющие высокие динамические параметры.

ИМС с эмиттерными связями ( ECL )

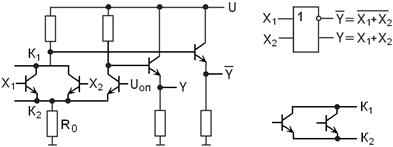

В базовом ECL-элементе ИЛИ, ИЛИ-НЕ обе логические операции (ИЛИ, НЕ) выполняются эмиттерно-связанными транзисторами, чем и обусловлено название типа логики. Элемент имеет два выхода, на одном из которых фиксируется результат операции ИЛИ, а на другом — операции ИЛИ-НЕ. Обозначают такой элемент ИЛИ, ИЛИ-НЕ.

Особенностью микросхем транзисторной логики с эмиттерными связями (ECL) является ненасыщенный режим работы транзисторов , что обеспечивает их высокое быстродействие. Вентильная ECL-ИМС выполняется на двух переключателях тока (рис. 5). Один из них, нормально открытый, реализован на транзисторе, на базу которого подано отпирающее напряжение U0 . Уровень U0 ниже минимального уровня логической 1. Второй переключатель тока состоит из m (по числу логических входов) транзисторов, имеющих общие коллекторы и эмиттеры, что обеспечивает реализацию функции ИЛИ. При отпирании любого транзистора второго переключателя тока, повышается уровень напряжения на общем эмиттерном резисторе R0 и обеспечивается запирание первого переключателя тока, что приводит к формированию на выходе Y высокого уровня (логическая 1), в то время как на выходе ![]() формируется низкий уровень (логический 0). Следовательно, по выходу

формируется низкий уровень (логический 0). Следовательно, по выходу ![]() реализуется функция ИЛИ-НЕ, а по входу Y — логическая функция ИЛИ.

реализуется функция ИЛИ-НЕ, а по входу Y — логическая функция ИЛИ.

|

|

|

|

Выполнение выходных каскадов логической схемы на эмиттерных повторителях (выходное сопротивление 30…50 Ом) обеспечивает большую нагрузочную способность базового элемента (n>10). Кроме того, при наличии эмиттерных повторителей смещается выходной уровень 1 элемента на величину падения напряжения на переходе кремниевого транзистора (Uбэ =0,7…0,8 В), создавая условия для ненасыщенного режима работы транзисторов последующей логической группы.

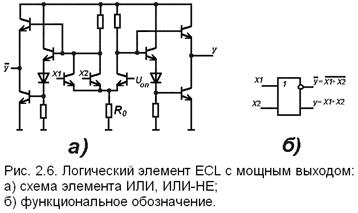

Рис. 6. Логический элемент ECL с мощным выходом:

а) схема элемента ИЛИ, ИЛИ-НЕ;

Транзисторы выходных эмиттерных повторителей работают в ненасыщенном режиме, так как напряжение на коллекторе всегда выше напряжения на базе и переходы коллектор-база никогда не оказываются смещенными в прямом направлении. Перепад напряжений логических уровней 1 и 0, как правило, находится в пределах 0,7…0,8 В, а помехоустойчивость составляет 0,15…0,2 В. За счет низкого выходного сопротивления уровень помех в линиях связи между элементами невысок, а постоянная токовая нагрузка элемента не вызывает всплесков напряжения в цепях питания. Наличие двух парафазных логических выходов в ECL-ИМС обеспечивает большую гибкость при проектировании цифровых устройств.

Увеличение коэффициента объединения по входам ИЛИ осуществляется за счет подключения к базовой ECL-ИМС логического расширителя. Однако на практике стремятся избежать применения логических расширителей, подключение которых существенно снижает быстродействие ИМС из-за значительных паразитных емкостей, что ограничивает параметр m в ECL БИС.

Для обеспечения высокой нагрузочной способности в состав серий ECL-ИМС включаются, микросхемы с мощным выходом (рис. 6), обеспечивающие n>30 при Cн >100 пФ. Возможна реализация ECL-ИМС, выходной каскад которой выполнен в виде повторителя со свободным эмиттером. Такая реализация выхода позволяет подключать в качестве нагрузки микросхемы с различными входными сопротивлениями. Это обеспечивает расширение логических возможностей по ИЛИ за счет объединения выходов ИМС без применения логических расширителей.

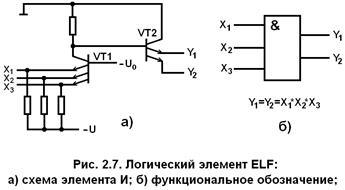

В качестве ЛЭ, дополняющих функциональные возможности типовых ECL-ИМС, применяются ИМС эмиттерной функциональной логики (EFL). Их особенностью является применение многоэмиттерных транзисторов (МЭТ), реализующих безынверсную функцию (рис. 7).

|

Применение в качестве выходного каскада элемента многоэмиттерного транзистора позволяет осуществлять соединение типа проводное ИЛИ и обеспечивает распараллеливание нагрузки.

Комбинация элементов EFL (функции И) с элементами ECL (функции ИЛИ-НЕ), которые хорошо согласуются в кристалле технологически и электрически, позволяет создавать узлы БИС с минимумов активных компонентов и более высоким функциональным быстродействием.

Большая потребляемая мощность элементов ECL является основным препятствием увеличения степени интеграции ECL-БИС, которая практически не может превысить 1000 вентилей в кристалле. При этом мощность рассеивания на кристалле может достигнуть 5…10 Вт, что потребует применения специальных конструктивных решений и систем охлаждения аппаратуры. Такими решениями могут быть теплоотводящие платы, радиаторы, охлаждающие жидкости и вентиляторы обдува, что значительно снизит эффект микроминиатюризации от внедрения БИС.

Важнейшее преимущество ECL-ИМС — наибольшее быстродействие по сравнению со всеми другими видами микросхем, а также высокая помехозащищенность благодаря значительным рабочим токам в цепях передачи информации определяют повсеместное применение ИМС в процессорах суперЭВМ с быстродействием до ![]() и более. К классу ECL (ЭСЛ) относятся, в частности, ИМС серий 100, 1500, 500.

и более. К классу ECL (ЭСЛ) относятся, в частности, ИМС серий 100, 1500, 500.

Интегральные элементы инжекционной логики (И2 Л)

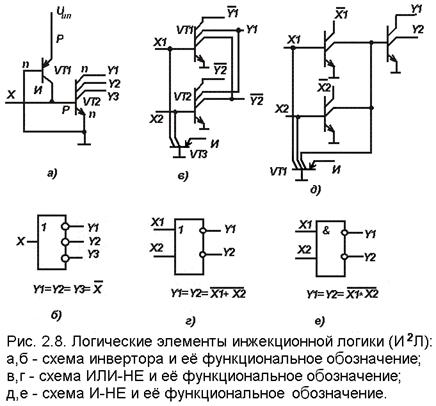

Схемы интегральной инжекционной логики (ИИЛ), или И2 Л-схемы, являются развитием схем с непосредственными связями (рис. 8).

Типовой И2 Л-вентиль содержит транзисторную структуру n-p-n, включенную по схеме с общим эмиттером и выполняющую роль выходного инвертирующего усилителя, обеспечивающего развязку выходов для исключения их взаимного влияния, а также дополняющую транзисторную структуру p-n-p, включенную по схеме с общей базой и служащую для инжекции тока в базу выходного усилителя. Соответственно транзистор VT1 называют инжектором , а VT2 — инвертором (рис. 8, а). Эти транзисторы в многоступенчатой логической схеме совмещаются в объеме полупроводника, причем база транзистора p-n-pесть эмиттер транзистора n-p-n, а коллекторы транзисторов p-n-p есть базовые области транзисторов n-p-n. Это обеспечивает высокую плотность упаковки элементов инжекционных микросхем на кристалле.

Типовые многовходовые И2 Л вентили с логикой ИЛИ-НЕ и И-НЕ приведены на рис. 8, в-е. Функция ИЛИ организуется объединением коллекторов выходных инвертирующих транзисторов, а функция И — подачей инверсных управляющих сигналов на входе и подключением дополнительного инвертирующего усилителя на выходе логической схемы.

|

Работа инжекционной микросхемы может быть рассмотрена на основе логического вентиля ИЛИ-НЕ (рис. 8, в, г). При уровнях логического 0 на входах X1 , X2 ток инжектора через многоколлекторный транзистор VT3 не сможет поступить в базы транзисторов VT1 , VT2 и они останутся запертыми, что приведет к формированию на выходе вентиля (Y1 и Y2 ) уровня 1. При поступлении логической 1 на любой из входов (это соответствует режиму запирания транзистора предшествующего каскада) инжектируемый ток через соответствующий коллектор транзистора VT3 поступит в базу транзистора схемы ИЛИ-НЕ (при X2 =1 ток поступит в базу транзистора VT2 ) и откроет его, что приведет к формированию логического 0 на выходах Y1 =Y2 =0. (Логику работы схемы И-НЕ (рис. 8, д, е) предполагается рассмотреть самостоятельно).

Быстродействие переключения инжекционных микросхем определяется током инжектора, увеличение которого до определенного значения позволяет уменьшить задержку срабатывания вентиля. Однако, при значительном увеличении тока инжектора из-за накопления больших избыточных зарядов в активных областях, задержка срабатывания резко возрастает.

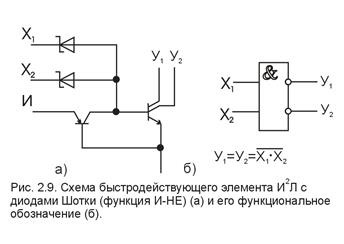

Повышение быстродействия реализуется при уменьшении геометрических размеров транзисторов, увеличении коэффициентов усиления, а также при создании И2 Л-ИМС с небольшими логическими перепадами уровней сигналов. Логический перепад можно снизить в 2…3 раза за счет применения диодов Шотки, включенных последовательно между выходом одного логического каскада и входом другого. Вариант включения диодов Шотки приведен на примере инвертора (рис. 9).

|

Важной проблемой проектирования БИС на инжекционных элементах является обеспечение необходимой помехоустойчивости. Типовые И2 Л-вентили имеют низкую помехоустойчивость к запирающим помехам (менее 0,1 В), что предопределило их использование преимущественно во внутренних узлах БИС. Для повышения помехоустойчивости во входных каскадах БИС применяют вентили с несколькими включенными последовательно базовыми диодами Шотки (помехоустойчивость к запирающим помехам увеличивается в 2…3 раза).