Реферат: Методы размещения и трассировки печатных плат на примере модуля памяти

б) Определяем множество вершин подключённых к базовой: {4;7}

Для каждой из вершин рассчитываем функционал по формуле:

Li=aij-pij

где aij – число связей вершины;

pij – число связей с базовой вершиной;

В нашем случае функционал равен:

L7=L4=2-1=1 ;

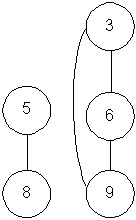

Для объединения с базовой вершиной необходимо выбрать вершину с наименьшим функционалом. Поскольку в нашем случае вершины Х7 и Х4 равнозначны, то объединяем их с Х1. Поскольку мощность блока (4 элемента 2И-НЕ в одной микросхеме) ещё не достигнута, а все оставшиеся вершины идентичны по отношению к вершине Х(1+4+7), дополним блок вершиной Х2, объединив их в одну микросхему. Получим граф:

|

Теперь, в качестве базовой изберём вершину Х3. Рассуждая так же как и в предыдущем шаге объединим в одну микросхему вершины Х3, Х6, Х9 и Х5. Вершину Х8 придётся поместить в отдельную микросхему.

Проанализировав полученные результаты можно увидеть, что для компоновки элементов Х1-Х9 необходимо 3 микросхемы КР1531ЛА3, причём в последней из них будет задействован лишь один элемент. В нашем случае рациональней будет уменьшить мощность блока до трёх. В этом случае количество необходимых микросхем не изменится, а элементы распределятся следующим образом: Х(1+4+7), Х(2+5+8), Х(3+6+9). Окончательно примем к проектированию именно такой вариант компоновки.

Три элемента 3И-НЕ поместим в одну микросхему КР1531ЛА3поскольку в этом случае мощность блока (кол-во элементов в микросхеме) равна количеству элементов в функциональной схеме.

На основании полученных результатов строим электрическую принципиальную схему блока оперативной памяти (см. графическую часть).

2. РАЗМЕЩЕНИЕ ЭРЭ НА МОНТАЖНОМ ПРОСТРАНСТВЕ.

В соответствии с заданием монтажное пространство — печатная плата 95х130 мм. Для размещения микросхем DD1—DD13 и разъема Х1 разобьем монтажное пространство на 14 посадочных мест, из которых место К14 отведем под разъем (рис.2.1).

К1 | К2 | К3 | К4 |

К5 | К6 | К7 |

К8 |

К9 | К10 | К11 | К12 |

К13 | К14 | ||

Рис. 2.1

Составим матрицу расстояний для приведённой платы:

| К1 | К2 | К3 | К4 | К5 | К6 | К7 | К8 | К9 | К10 | К11 | К12 | К13 | К14 | |

| К1 | 0 | 1 | 2 | 3 | 1 | 2 | 3 | 4 | 2 | 3 | 4 | 5 | 3 | 4 |

| К2 | 1 | 0 | 1 | 2 | 3 | 1 | 2 | 3 | 3 | 2 | 3 | 4 | 4 | 3 |

| К3 | 2 | 1 | 0 | 1 | 3 | 2 | 1 | 2 | 4 | 3 | 2 | 3 | 4 | 3 |

| К4 | 3 | 2 | 1 | 0 | 4 | 3 | 2 | 1 | 5 | 4 | 3 | 2 | 4 | 3 |

| К5 | 1 | 2 | 3 | 4 | 0 | 1 | 2 | 3 | 1 | 2 | 3 | 4 | 2 | 3 |

| К6 | 2 | 1 | 2 | 3 | 1 | 0 | 1 | 2 | 2 | 1 | 2 | 3 | 3 | 2 |

| К7 | 3 | 2 | 1 | 2 | 2 | 1 | 0 | 1 | 3 | 2 | 1 | 2 | 3 | 2 |

| К8 | 4 | 3 | 2 | 1 | 3 | 2 | 1 | 0 | 4 | 3 | 2 | 1 | 3 | 2 |

| К9 | 2 | 3 | 4 | 5 | 1 | 2 | 3 | 4 | 0 | 1 | 2 | 3 | 1 | 2 |

| К10 | 3 | 2 | 3 | 4 | 2 | 1 | 2 | 3 | 1 | 0 | 1 | 2 | 2 | 1 |

| К11 | 4 | 3 | 2 | 3 | 3 | 2 | 1 | 2 | 2 | 1 | 0 | 1 | 2 | 1 |

| К12 | 5 | 4 | 3 | 2 | 4 | 3 | 2 | 1 | 3 | 2 | 1 | 0 | 2 | 1 |

| К13 | 3 | 4 | 4 | 4 | 2 | 3 | 3 | 3 | 1 | 2 | 2 | 2 | 0 | 1 |

| К14 | 4 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 0 |

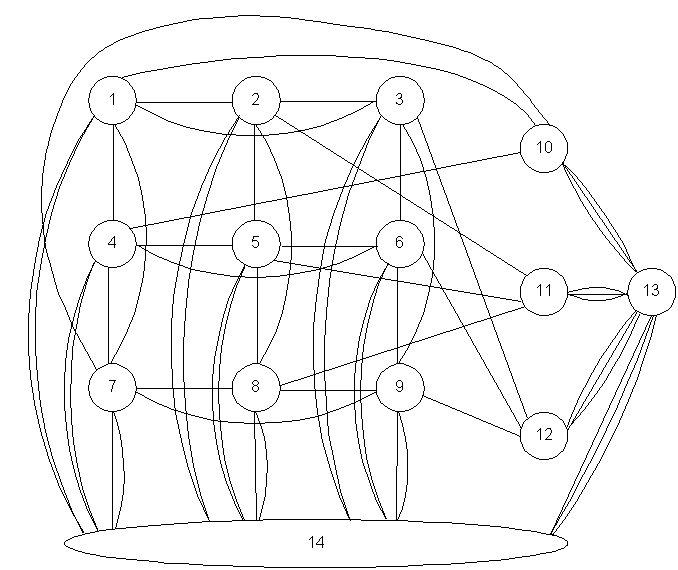

Приведём полный граф электрической принципиальной схемы (рис. 2.2). Элементы 1…12 – микросхемы КР1531ЛА3, элемент 13 – микросхема КР1531ЛА4, а элемент 14 – разъём.

рис. 2.2.

Матрица смежности этого графа имеет вид:

| К1 | К2 | К3 | К4 | К5 | К6 | К7 | К8 | К9 | К10 | К11 | К12 | К13 | К14 | |

| К1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 2 |

| К2 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 2 |

| К3 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 2 |

| К4 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 2 |

| К5 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 2 |

| К6 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 2 |

| К7 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 2 |

| К8 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 2 |

| К9 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 2 |

| К10 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 3 | 0 |

| К11 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 3 | 0 |

| К12 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 3 | 0 |

| К13 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 3 | 3 | 3 | 1 | 3 |

| К14 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 0 | 0 | 0 | 3 | 1 |

Для размещения корпусов микросхем на печатной плате воспользуемся последовательным алгоритмом размещения:

1) Устанавливаем в какую-либо позицию любой из элементов.

2) Выбираем элемент для установки на текущем шаге. Для этого определяем коэффициент связности всех не установленных элементов с ранее установленными (по матрице смежности):

(2.1)

(2.1)

где aij – число связей с ранее установленными элементами;

Vi – общее число связей элемента;

2) Выбираем элемент с максимальным коэффициентом связности Ф .

3) Пытаемся установить выбранный элемент в одну из незанятых позиций. Считаем для этой позиции D F по формуле:

![]() (2.2)

(2.2)

где aij – количество связей между i-м и j-м элементами;

rij – расстояние между элементами, берётся из матрицы расстояний;

fij – элемент матрицы весовых коэффициентов;

4) Повторяем пункт 3 для всех свободных позиций на печатной плате. Окончательно устанавливаем выбранный элемент в позицию с минимальным D F .

5) Повторяем пункты 2 - 4 пока не установим все элементы.

Произведём размещение элементов по вышеописанному алгоритму.

В нашем случае, поскольку все элементы равноправны, матрица весовых коэффициентов в формуле 2.2 будет единичной, поэтому этот параметр мы указывать не будем. В первую очередь установим разъём в позицию К14, т.к. его положение жёстко определено конструкторскими ограничениями.

Вычислим коэффициенты связности:

Ф1 =Ф2 =Ф3 =Ф4 =Ф5 =Ф6 =Ф7 =Ф8 =Ф9 =2/7;

Ф10 =Ф11 =Ф12 =0\6=0;

Ф13 =3/12;

Выбираем элемент DD1. Поскольку позиции К10,К11,К12 и К13 равноценны с точки зрения минимума длинны связи с разъёмом, то установим DD1 в позицию К13.