Реферат: Методы размещения и трассировки печатных плат на примере модуля памяти

ВВЕДЕНИЕ................................................................................................................ 2

1. ВЫБОР СЕРИИ И ТИПОВ МИКРОСХЕМ И РАСПРЕДЕЛЕНИЕ ЭЛЕМЕНТОВ ФУНКЦИОНАЛЬНОЙ СХЕМЫ ПО КОРПУСАМ.................. 3

1.1. Выбор физических элементов для реализации схемы и обзор параметров выбранной серии..................................................................................................... 3

1.2. Распределение элементов функциональной схемы по корпусам............ 4

2. РАЗМЕЩЕНИЕ ЭРЭ НА МОНТАЖНОМ ПРОСТРАНСТВЕ..................... 6

3. ТРАССИРОВКА МОНТАЖНЫХ СОЕДИНЕНИЙ...................................... 10

3.1 Трассировка с помощью алгоритма Прима............................................... 10

3.2 Трассировка по алгоритму Краскала.......................................................... 12

3.3 Трассировка классическим волновым алгоритмом Ли............................ 14

ЗАКЛЮЧЕНИЕ....................................................................................................... 15

ЛИТЕРАТУРА......................................................................................................... 16

ВВЕДЕНИЕ

Основные принципы изготовления и применения печатных схем стали известны в начале ХХ века, однако промышленный выпуск печатных схем и плат был организован лишь в начале 40-х годов.

С переходом на микроэлектронные элементы, резким уменьшением размеров и возрастанием быстродействия схем первое место занимают вопросы обеспечения постоянства характеристик печатных проводников и взаимного их расположения. Значительно усложнились задачи проектирования и оптимального конструирования печатных плат и элементов.

Печатные платы нашли широкое применение в электронике, позволяя увеличить надёжность элементов, узлов и машин в целом, технологичность (за счёт автоматизации некоторых процессов сборки и монтажа), плотность размещения элементов (за счёт уменьшения габаритных размеров и массы), быстродействие, помехозащищённость элементов и схем. Печатный монтаж – основа решения проблемы компановки микроэлектронных элементов. Особую роль печатные платы играют в цифровой микроэлектронике. В наиболее развитой форме (многослойный печатный монтаж) он удовлетворяет требования конструирования вычеслительных машин третьего и последующих поколений.

При разработке конструкции печатных плат проектеровщику приходится решать схемотехнические (минимизация кол-ва слоёв, трассировка), радиотехнические (расчёт паразитных наводок), теплотехнические (температурный режим работы платы и элементов), конструктивные (размещения), технологические (выбор метода изготовления) задачи.

В данном курсовом проекте при разработке печатной платы мы попытались показать методы решения лишь схемотехнических и технологических задач.

1. ВЫБОР СЕРИИ И ТИПОВ МИКРОСХЕМ И РАСПРЕДЕЛЕНИЕ ЭЛЕМЕНТОВ ФУНКЦИОНАЛЬНОЙ СХЕМЫ ПО КОРПУСАМ.

1.1. Выбор физических элементов для реализации схемы и обзор параметров выбранной серии .

Выбор серии интегральных микросхем для реализации блока оперативной памяти в первую очередь продиктован скоростью работы такого блока. В этом отношении микросхемы серии ТТЛШ (транзисторно–транзисторная логика со структурой Шотки) наиболее предпочтительны.

Электрическая функциональная схема блока оперативной памяти содержит сорок пять элементов 2И-НЕ, три элемента 3И-НЕ.

Для реализации блока оперативной памяти выбираем следующие типы микросхемы:

две микросхемы серии КР1531ЛА3 (корпус содержит 4 элемента 2И-НЕ);

две микросхемы серии КР1531ЛА4 (корпус содержит 3 элемента 3И-НЕ);

Основные параметры микросхем ТТЛШ серии КР1531:

— напряжение питания Uип = 5В ± 10%;

— выходное напряжение низкого уровня не более U0 вых = 0,5В;

— выходное напряжение высокого уровня не менее U1 вых = 2,5В;

— время задержки распространения tзд.р. = 4,5нс;

— потребляемая мощность Pпот = 4мВт;

— сопротивление нагрузки Rн = 0,28кОм;

1.2. Распределение элементов функциональной схемы по корпусам.

Распределение четырёх элементов 2И-НЕ составляющих триггер очевидно:

Поскольку внутренних связей в таком элементе гораздо больше чем внешних, то очевидно их помещение в одну микросхему КР1531ЛА3.

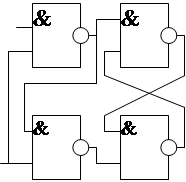

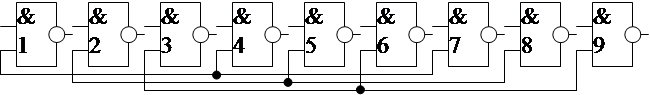

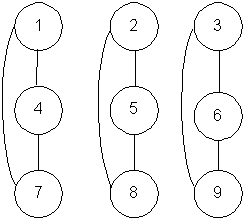

Для распределения девяти оставшихся элементов 2И-НЕ по трём корпусам микросхем КР1531ЛА3 вычерчиваем часть электрической функциональной схемы блока оперативной памяти, содержащую эти элементы, и строим соответствующий ей граф G1 (рис.1.1).

|

???. 1.1

--> ЧИТАТЬ ПОЛНОСТЬЮ <--