Реферат: Обработка изображений с использованием расширения процессора

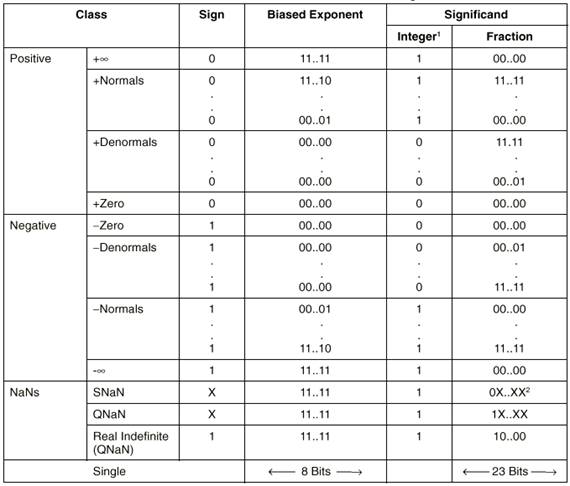

Таблица 2-2. Вещественные числа и кодирование NaN

SIMD регистр состояния и управления

Регистр состояния и управления используется для установки флагов обнаружения арифметических исключений, флагов режимов обработки арифметических исключений, режима округления, режима flush-to-zero и для просмотра флага состояния. Содержимое этого регистра может быть загруженно с помощью инструкций LDMXCSR и FXRSTOR и сохранено в памяти с помощью инструкций STMXCSR и FXSAVE.

Биты 0-5 (поле обнаружения исключений)содержат 6 флагов, которые служат признаками детектирования арифметических SIMD исключений с плавающей точкой (0-нет, 1-да). Исключение произойдет только после следующей команды SSE. Потоковое расширение SSE использует только один флаг исключения для каждой исключительной ситуации. Здесь не предоставляется возможность для уведомления об индивидуальных исключительных ситуациях внутри упакованных данных. В ситуации, когда происходит несколько идентичных исключительных ситуаций в одной инструкции, соответствующий флаг исключения обновляется и указывает, что хотя бы одно из этих условий произошло. По умолчанию эти флаги сбрасываются.

Биты 7-12 (поле маскирования исключений) определяют, как обрабатываются обнаруженные исключения. Если флаг установлен, то соответствующее исключение маскировано и обрабатывается процессором, который формирует приемлемый результат (в соответствии с процедурой, установленной по умолчанию) и продолжает выполнение программы. Если флаг сброшен, то вызывается программный обработчик для этого исключения. По умолчанию флаги устанавливаются в 1, значит что все исключения маскированы.

Биты 13-14 (RC) устанавливают режим округления результатов при выполнении SSE-команд над данными с плавающей точкой. По умолчанию устанавливается режим округление до ближайшего.

Бит 15 (FZ) используется для включения режима “Flush To Zero”. По умолчанию бит 15 установлен в 0, что выключает режим “Flush To Zero”.

Остальные биты регистра MXCSR (биты 16-31 и бит 6) определены как зарезервированные и установлены в 0; попытка записи не нулевых значений в эти биты, используя инструкцию FXRSTOR или LDMXCSR, вызовет исключение общего нарушения защиты (general protection exception).

Поле управления округлением

Поле управления округлением (RC) регистра MXCSR (биты 13 и 14) управляют как округляется результат инструкции с плавающей точкой.

Поддерживается четыре режима округления:

· округление до ближайшего

· до меньшего или равного

· до большего или равного

· и в сторону нуля (смотреть таблицу 2-3).

Округление до ближайшего - режим по умолчанию и он подходит для большинства приложений. Он обеспечивает наиболее точный и статистически несмещенную оценку правильного результата.

Таблица 2-3. Поле управления округлением (RC)

| Режим округления | Установка полей RC | Описание |

| Округление до ближайшего | 00B | Результатом округления берется наилучшее приближение до точного результата. Если два значения одинаково близки к точному результату, то берется четное значение (то есть, то значение у которого наименьший значащий разряд установлен в ноль) |

| Округление до меньшего или равного (в сторону -) | 01B | Результат округления ближайшее, но не больше чем точное решение. |

| Округление до большего или равного (в сторону +) | 10B | Результат округления ближайшее, но не меньше чем точное решение. |

| Округление в сторону нуля (усечение) | 11B | Результат округления ближайшее, но не больше чем абсолютное значение точного решения. |

Команды Потокового Расширения SIMD

Потоковое Расширение SIMD состоит из 70 команд, сгруппированных в следующие категории:

· Команды копирования данных

· Арифметические команды

· Команды сравнения

· Команды преобразования типов данных

· Логические команды

· Дополнительные целочисленные SIMD-команды

· Команды перестановки

· Команды управления состоянием

· Команды управления кэшированием

Операнды команд

Параллельные операции, как правило, действуют одновременно на все четыре 32-разрядных элемента данных в каждом из 128-разрядных операндов В именах команд, выполняющих параллельные операции, присутствует суффикс ps. Например, команда addps складывает 4 пары элементов данных и записывает полученные 4 суммы в соответствующие элементы первого операнда.

Скалярные операции действуют на младшие (занимающие разряды 0-31) элементы данных двух операндов Остальные три элемента данных в выходном операнде не изменяются (исключение составляет команда скалярного копирования movss). В имени команд, выполняющих скалярные операции, присутствует суффикс ss (например, команда addss).

Большинство команд имеют два операнда. Данные, содержащиеся в первом операнде, могут использоваться командой, а после ее выполнения, как правило, замещаются результатами. Данные во втором операнде используются в команде и после ее выполнения не изменяются. Далее в тексте входным называется второй операнд, а выходным – первый.