Реферат: Последовательностные функциональные узлы

Содержание

1. Общая структура последовательностного устройства

2. Синхронные триггеры

3. Порядок синтеза последовательностного устройства

Библиографический список

1. Общая структура последовательностного устройства

Цифровое устройство, в котором состояние выхода зависит не только от того, какие сигналы присутствуют на его входах в данное время, но и от того, какие последовательности сигналов поступали на входы устройства в предшествующие моменты времени, называют цифровым автоматом. Такие устройства за их способность запоминать последовательности входных или выходных сигналов называют также последовательностными устройствами.

![]()

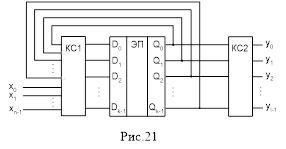

Цифровые автоматы, применяемые в цифровой технике, преимущественно строятся по общей схеме, приведенной на рис.1. Такие автоматы называют автоматами Мура. На рис.21: ЭП – элементы памяти (регистр) c входами D0 ,...,Dk -1 и выходами Q0 ,...,Qk -1 . КС1 вырабатывает входные сигналы для элементов памяти, используя для этого их текущие состояния выходов (коды Q0 ,...,Qk -1 ) и внешние сигналы x0 ,...,xn -1 (коды настройки на определенный режим работы, сигналы синхронизации и т.п.). КС2 преобразует внутренние рабочие коды состояния устройства Q0 ,...,Qk -1 в выходные коды y0 ,...,yk -1 .

Состояния всех входов, элементов памяти и выходов рассматриваются в одинаковые дискретные моменты времени. В зависимости от того, как эти моменты времени определены, последовательностные устройства разделяются на синхронные и асинхронные.

В синхронных устройствах дискретные моменты времени задают специальные синхронизирующие сигналы (импульсы), поступающие от некоторого независимого источника синхронизации. В синхронных последовательностных устройствах, следовательно, длительность рабочего такта задается синхронизирующими сигналами.

В отличие от синхронного, в асинхронном последовательностном устройстве дискретные моменты времени определяются моментами изменения состояния входа или состояния памяти, а длительность рабочих тактов определяется интервалом времени, в течение которого состояние автомата не меняется.

Таким образом, работу цифрового автомата Мура (рис.1) можно определить следующими логическими уравнениями

Qt+1 =f1 (Qt ,X t ), Y t =f2 (Qt ), (14)

где Qt – k-разрядное число, определяющее состояние памяти автомата в дискретное время t (текущее состояние памяти); Xt – n-разрядное число, определяющее состояние входов в дискретное время t (текущее состояние входов); Qt +1 – k-разрядное число, определяющее состояние памяти в дискретное время t+1 (последующее состояние памяти); Yt – l-разрядное число, определяющее состояние выходов в дискретное время t (текущее состояние выходов).

2. Синхронные триггеры

В качестве элементов памяти в схеме цифрового автомата рис.1 используются триггеры, включенные определенным образом в структуру памяти для обеспечения выполнения его функций.

Используемые в цифровой технике триггеры представляют собой электронные схемы, имеющие два устойчивых состояния. Эти состояния устанавливаются при подаче соответствующей комбинации сигналов на входы триггера и сохраняются после окончания действия этих сигналов.

Состояние триггера описывается значением выходного сигнала Q. Это состояние определяется (задается) комбинацией входных сигналов на информационных входах триггера. Если при изменении сигналов на информационных входах соответствующее изменение Q, т.е. переключение триггера происходит только при поступлении синхронизирующего сигнала (импульса) на специальный вход синхронизации С, то триггер называется синхронным. Триггеры могут переключаться по уровню или по фронту синхроимпульса.

Триггеры, переключающиеся по уровню, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих информационных сигналов, т.е. могут переключиться несколько раз за время действия одного синхроимпульса. В течение паузы между синхроимпульсами состояние такого триггера сохраняется при любых изменениях информационных сигналов.

Триггеры, переключающиеся по фронту, изменяют свое состояние при поступлении на синхронизирующий вход соответствующего фронта синхроимпульса (положительного или отрицательного). За время действия одного синхроимпульса триггер, синхронизируемый фронтом, может переключиться только один раз.

В асинхронных триггерах отсутствует вход синхронизации. Поэтому переключение асинхронных триггеров происходит, как только на информационные входы поступает соответствующая переключающая комбинация сигналов.

В цифровой технике наиболее часто используются SR-, JK-, D-, T-триггеры. Обозначающие тип триггера буквы раскрывают функциональное назначение информационных (управляющих) входов триггера:

S – вход установки в состояние 1;

R – вход установки в состояние 0;

J – вход переключения из состояния 0 в состояние 1;

K – вход переключения из состояния 1 в состояние 0;

D – информационный вход для установки состояния 1 или 0;

T – вход инвертирования состояния триггера (счетный вход).

Функциональные возможности триггера описывают его характеристическая таблица (таблица состояний) и характеристическое уравнение. Для перечисленных типов триггеров они приведены на рис.2. Таблица состояний и уравнение определяют логическую зависимость последующего состояния триггера Qt +1 от текущих значений сигналов на информационных входах и текущего состояния триггера Qt .

![]()

SR-триггер. При S = R = 0 триггер работает в режиме хранения, т.е. сохраняет ранее установленное состояние Qt +1 = Qt . При S = 1, R = 0 триггер устанавливается в состояние Qt +1 = 1, а при S = 0, R = 1 – в состояние Qt +1 = 0. Комбинация входных сигналов S = R = 1 (установка 1 и 0 одновременно) является запрещенной, так как приводит к непредсказуемому состоянию триггера после поступления синхроимпульса. Во избежание возникновения сбоев комбинацию S = R = 1 исключают, поэтому она является нереализуемой.

Характеристическое уравнение SR-триггера, приведенное на рис.2, легко получить путем минимизации логической функции Qt +1 (St ,Rt ,Qt ) с использованием карты Карно.

--> ЧИТАТЬ ПОЛНОСТЬЮ <--