Реферат: Разработка для контроля и определения типа логических интегральных микросхем методом сигнатурного анализа

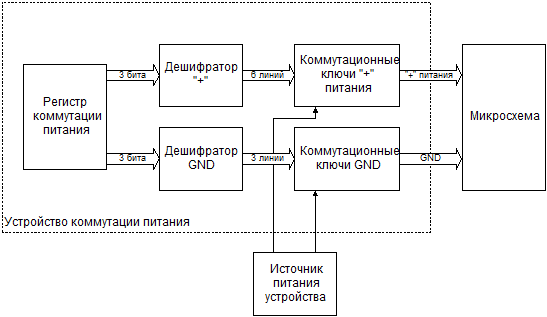

3) коммутационные ключи по «+» питания;

4) коммутационные ключи по GND.

Структурная схема устройства коммутации приведена на рис.4.

Рис.4. Структурная схема устройства коммутации питания ИМС.

4. Выбор технических и программных средств реализации.

4.1. Выбор элементной базы.

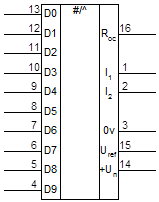

Для реализации программного управления напряжением питания и током потребления ИМС в качестве ЦАП выбран К572ПА1А, отвечающий требованиям разрядности (>=8 бит) и быстродействия (<100мкс).

Микросхема представляет собой умножающий ЦАП, выполненный по КМОП технологии. Предназначена для преобразования параллельного 10-разрядного двоичного кода на цифровых входах в ток на аналоговом выходе, который пропорционален значениям кода и (или) опорного напряжения.

Микросхема поставляется в герметичном 16-выводном металлокерамическом корпусе типа 201.16-8 с двухрядным вертикальным расположением выводов.

Электрические параметры ЦАП К572ПА1А приведены в табл.1, условное графическое обозначение на рис.5, назначение выводов - в табл.2.

Таблица 1

| Номинальное напряжение питания | 15в |

| Ток потребления | 3 мА |

| Дифференциальная нелинейность | +0.1% |

| Погрешность коэффициента преобразования | +3% |

| Время установления выходного тока | 5 мкс |

| Среднее значение входного тока по цифровым входам | 1 мкА |

| Выходной ток при опорном напряжении 10В | 2 мА |

| Предельные значения опорного напряжения | +17в |

| Предельные значения напряжения питания | 5...17в |

К572ПА1А

Рис.5. ЦАП К572ПА1А (обозначение).

Таблица 2

| 1 | 1-й аналоговый выход |

| 2 | 2-й аналоговый выход |

| 3 | общий |

| 4 | 10-й цифровой вход (старший значащий разряд) |

| 5 | 9-й цифровой вход |

| 6 | 8-й цифровой вход |

| 7 | 7-й цифровой вход |

| 8 | 6-й цифровой вход |

| 9 | 5-й цифровой вход |

| 10 | 4-й цифровой вход |

| 11 | 3-й цифровой вход |

| 12 | 2-й цифровой вход |

| 13 | 1-й цифровой вход (младший значащий разряд) |

| 14 | “+” питания |

| 15 | опорное напряжение |

| 16 | вывод резистора обратной связи |

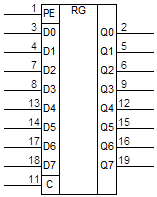

Для запоминания выставленных значений в качестве входных регистров необходимы 8-битные параллельные регистры-защелки с суммарным числом запоминаемых битов - 32. Эти регистры должны иметь тактируемый вход записи, вход разрешения параллельной загрузки, быстродействие <100мкс, не должны иметь Z-состояния (чтобы не было неопределенных уровней сигналов). Этим требованиям соответствуют 4 регистра К555ИР27.

В качестве регистров коммутации, управления напряжением и током можно выбрать К555ИР27, поскольку они обеспечивают необходимую разрядность (8 бит), управление (запись/запоминание/хранение) и быстродействие.

Микросхема выполнена в пластмассовом корпусе 1400.20-2 с двухрядным вертикальным расположением выводов.

Электрические параметры микросхемы К555ИР27 приведены в табл.3, условное графическое обозначение на рис.6, назначение выводов - в табл.4, состояния регистра ИР27 - в табл.5.

Таблица 3

| Uпит., ном., В | 5 |

| U0 вых. , не более, В | 0.5 |

| U1 вых. , не менее, В | 2.7 |

| I0 вх. , не более, мА | -0.4 |

| I1 вх. , не более, мА | 0.02 |

| Iпот. , не более, мА | 28 |

| t1.0 зд.р. , не более, нс | 30 |

| t0. 1 зд.р. , не более, нс | 30 |

К555ИР27

Рис.6. Регистр К555ИР27 (обозначение).

Таблица 4

| 1 | Вход разрешения параллельной загрузки /PE |

| 2 | Выход данных Q0 |

| 3 | Вход данных Q0 |

| 4 | Вход данных Q1 |

| 5 | Выход данных Q1 |

| 6 | Выход данных Q2 |

| 7 | Вход данных Q2 |

| 8 | Вход данных Q3 |

| 9 | Выход данных Q3 |

| 10 | GND |

| 11 | Синхронный тактовый вход C |

| 12 | Выход данных Q4 |

| 13 | Вход данных Q4 |

| 14 | Вход данных Q5 |

| 15 | Выход данных Q5 |

| 16 | Выход данных Q6 |

| 17 | Вход данных Q6 |

| 18 | Вход данных Q7 |

| 19 | Выход данных Q7 |

| 20 | “+” питания |

Таблица 5

| Режим работы | Вход C | Вход /PE | Вход Dn | Выход Qn |

| Загрузка “1” | | 0 | 1 | 1 |

| Загрузка “0” | | 0 | 0 | 0 |

| Хранение | | 1 | X | Qn’ |

| X | 1 | X | Qn’ |

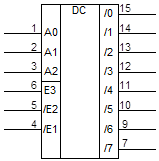

В качестве управляющего устройства необходим дешифратор с количеством входов 3, количеством выходов не менее 7 и быстродействием <100мкс. Этим требованиям соответствует микросхема К555ИД7. Это двоично-десятичный дешифратор-демультиплексор, преобразующий трехразрядный код A0...A2 в напряжение низкого уровня, появляющееся на одном из восьми выходов /0.../7. Эту же микросхему можно выбрать в качестве дешифратора в устройстве коммутации питания как в цепи “+” питания, так и в цепи GND.

Микросхема выполнена в пластмассовом корпусе 238.16-2 с двухрядным вертикальным расположением выводов.

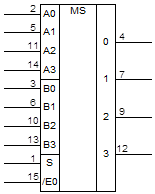

Электрические параметры микросхемы К555ИД7 приведены в табл.6, условное графическое обозначение на рис.7, назначение выводов - в табл.7, состояния регистра ИР27 - в табл.8.

Таблица 6

| Uпит., ном., В | 5 |

| U0 вых. , не более, В | 0.48 |

| U1 вых. , не менее, В | 2.9 |

| I0 вх. , не более, мА | -0.36 |

| I1 вх. , не более, мА | 0.02 |

| Iпот. , не более, мА | 10 |

| t1.0 зд.р. , не более, нс | 41 |

| t0. 1 зд.р. , не более, нс | 27 |

К555ИД7

Рис.7. Дешифратор К555ИД7 (обозначение).

Таблица 7

| 1 | Вход данных A0 |

| 2 | Вход данных A1 |

| 3 | Вход данных A2 |

| 4 | Вход разрешения /E1 |

| 5 | Вход разрешения /E2 |

| 6 | Вход разрешения E3 |

| 7 | Выход данных /7 |

| 8 | GND |

| 9 | Выход данных /6 |

| 10 | Выход данных /5 |

| 11 | Выход данных /4 |

| 12 | Выход данных /3 |

| 13 | Выход данных /2 |

| 14 | Выход данных /1 |

| 15 | Выход данных /0 |

| 16 | “+” питания |

Таблица 8

| Входы | Выходы | ||||||||||||||||||||||||

| /E1 | /E2 | E3 | A0 | A1 | A2 | /0 | /1 | /2 | /3 | /4 | /5 | /6 | /7 | ||||||||||||

| 1 | X | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| X | 1 | X | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| X | X | 0 | X | X | X | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | ||||||||||||

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | ||||||||||||

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | ||||||||||||

Для считывания данных с выводов испытуемой микросхемы (для перевода 4-битного кода в 8-битный) необходимы двухвходовые 4-канальные мультиплексоры без инверсии, с суммарным числом считываемых бит - 32и быстродействием <100мкс. Этим требованиям соответствуют 4 микросхемы К555КП11.

Микросхема выполнена в пластмассовом корпусе 238.16-2 с двухрядным вертикальным расположением выводов.

Электрические параметры микросхемы К555КП11 приведены в табл.9, условное графическое обозначение на рис.8, назначение выводов - в табл.10, состояния мультиплексора КП11 - в табл.11.

Таблица 9

| Uпит., ном., В | 5 |

| U0 вых. , не более, В | 0.48 |

| U1 вых. , не менее, В | 2.5 |

| I0 вх. , не более, мА | -0.76 |

| I1 вх. , не более, мА | 0.02 |

| I0 пот. , не более, мА | 13.6 |

| I1 пот. , не более, мА | 9.7 |

| t1.0 зд.р. , не более, нс | 21 |

| t0. 1 зд.р. , не более, нс | 18 |

К555КП11

Рис.8. Мультиплексор К555КП11 (обозначение).

Таблица 10

| 1 | Входадреса данных S |

| 2 | Вход данных I 1a |

| 3 | Вход данных I2a |

| 4 | Выход данных Ya |

| 5 | Вход данных I1b |

| 6 | Вход данных I2b |

| 7 | Выход данных Yb |

| 8 | GND |

| 9 | Выход данных Yc |

| 10 | Вход данных I1c |

| 11 | Вход данных I2c |

| 12 | Выход данных Yd |

| 13 | Вход данных I1d |

| 14 | Вход данных I2d |

| 15 | Вход разрешения трансляции данных на выходы /E0 |

| 16 | “+” питания |

Таблица 11

| Входы | Выходы | ||||||

| /E0 | S | I1 | I2 | Y | |||

| 1 | X | X | X | Z | |||

| 0 | 0 | 0 | X | 0 | |||

| 0 | 0 | 1 | X | 1 | |||

| 0 | 1 | X | 0 | 0 | |||

| 0 | 1 | X | 1 | 1 | |||

4.2. Выбор программных средств.

В настоящее время существует большой выбор различных программных средств. При этом каждое из них имеет свою область применения. Например, для написания системных драйверов используются языки программирования низкого уровня (Assembler, Forth), так как работа таких программ идет в реальном времени, и для своевременной обработки данных требуется большое быстродействие драйвера-программы. Для написания удобных интерфейсов программ, а также программ, связанных с ведением баз данных, где не требуется столь высокого быстродействия, используются языки программирования высокого уровня (Clipper, Pascal, FoxPro, C++, Visual Basic). Т.е. выбор тех или иных программных средств реализации зависит конкретно от поставленной задачи и возлагаются на программиста, решающего эту задачу.

При проектировании данного устройства, для написания подпрограмм обмена информацией между проектируемым устройством и компьютером было решено использовать Assembler(процессора 80286), поскольку он обеспечивает максимальное быстродействие,минимальный объем, а также простоту и удобство в написании подпрограмм подобного класса.

При этом сохраняется возможность использования для этой цели морально устаревших в настоящее время компьютеров на базе процессоров 80286 и 80386, имеющихся в достаточном количестве на предприятиях, работающих в операционной системе MS-DOS.Также (при использовании соответствующих микропроцессоров и программных средств) этим обеспечивается максимальная транспортабельность программы при создании интерфейсов под другие операционные системы (OS/2, Windows95, Windows NT, Unix и пр.).

Ассемблер представляет собой язык программирования низкого уровня, в котором программист пишет инструкции, управляющие работой процессора. При помощи программы-компилятора эти инструкции переводятся в машинный код, исполняемый непосредственно процессором. В число команд Ассемблера входит самый минимальный набор (команды перехода, вызова подпрограмм и возврата из них, работы с регистрами, памятью, арифметические операции, логические операции, операции сдвига,сравнения, работы с портами ввода/вывода).

Для написания интерфейса программы поддержки данного устройства возможно использование любого из языков программирования высокого уровня, позволяющего вставлять подпрограммы на Ассемблере в текст программы.Поскольку данный вопрос выходит за рамки настоящей работы, подробно он рассматриваться не будет [8,9].

5. Описание принципиальных схем.

5.1. Описание состава принципиальных схем в сопоставлении с соответствующими структурными схемами узлов.

После выяснения структуры устройства и выбора элементной базы можно приступать к проектированию принципиальной схемы.

1) Входные регистры (см. структурную схему на рис.2).

Данный узел представляет собой 32-разрядный запоминающий регистр с ТТЛ-уровнями, без Z-состояния, использующий 8 входных линий данных и несколько линий управления на 32 выходных линии. Принципиальная схема узла изображена на рис.9.