Реферат: Технические характеристики современных серверов

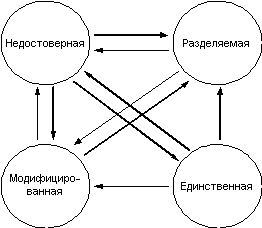

Состояние строки "Разделяемая" (Shared):

Данные этой строки достоверны в данном кэше, а также в одном или нескольких удаленных кэшах.

Состояние строки "Модифицированная" (Modified):

Данные этой строки достоверны только в данном кэше и были модифицированы. Данные недостоверны в памяти.

Состояние строки "Недостоверная" (Invalid):

Достоверные данные не были найдены в данном кэше.

Рис. 4.4. Диаграмм переходов состояний протокола MESI

Для поддержки мультипроцессорной организации были реализованы несколько примитивов адресной шины. Это позволяет одному главному устройству шины передавать, а другим устройствам обнаруживать (или наблюдать) появление этих примитивов на шине. Устройство-владелец кэша наблюдает за адресной шиной во время глобального запроса и сравнивает целевой адрес с адресами тегов в своем кэше L2. Если происходит попадание, то выполняемые действия определяются природой запроса.

Как уже было отмечено, одной из функций тегов L2 является уменьшение накладных расходов, связанных с ответами на запросы механизма наблюдения. Доступ к тегам L2 разделяется между процессорами и адресной шиной. Теги L2 практически выполняют роль фильтров по отношению к активностям наблюдения. Это позволяет процессорам продолжать обработку вместо того, чтобы отвечать на каждый запрос наблюдения. Хотя теги L2 представляют собой разделяемый между процессором и шиной ресурс, его захват настолько кратковременен, что практически не приводит ни к каким конфликтам.

Состояние строки кэш-памяти "модифицированная" означает в частности то, что кэш, хранящий такие данные, несет ответственность за правильность этих данных перед системой в целом. Поскольку в основной памяти эти данные недостоверны, это означает, что владелец такого кэша должен каким-либо способом гарантировать, что никакой другой модуль системы не прочитает эти недостоверные данные. Обычно для описания такой ответственности используется термин "вмешательство" (intervention), которое представляет собой действие, выполняемое устройством-владельцем модифицированных кэшированных данных при обнаружении запроса наблюдения за этими данными. Вмешательство сигнализируется с помощью ответа состоянием "строка модифицирована" протокола MESI, за которым следуют пересылаемые запросчику, а также потенциально в память, данные.

Для увеличения пропускной способности системы в PowerScale реализованы два способа выполнения функции вмешательства:

- Немедленная кроссировка (Cross Immediate), которая используется когда канал данных источника и получателя свободны и можно пересылать данные через коммутатор на полной скорости.

- Поздняя кроссировка (Cross Late), когда ресурс (магистраль данных) занят, поэтому данные будут записываться в буфер коммутатора и позднее пересылаться запросчику.

Физическая реализация архитектуры

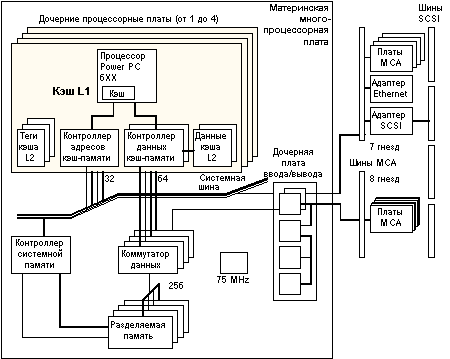

Ниже на рис. 4.5 показана схема, представляющая системные платы, разработанные компанией Bull, которые используются для физической реализации архитектуры PowerScale.

Многопроцессорная плата:

Многопроцессорная материнская плата, которая используется также в качестве монтажной панели для установки модулей ЦП, модулей основной памяти и одной платы в/в (IOD).

Модуль ЦП (дочерняя процессорная плата):

Каждый модуль ЦП, построенный на базе PowerPC 601/604, включает два микропроцессора и связанные с ними кэши. Имеется возможность модернизации системы, построенной на базе процессоров 601, путем установки модулей ЦП с процессорами 604. Смешанные конфигурации 601/604 не поддерживаются.

Дочерняя плата ввода/вывода: (IOD)

IOD работает в качестве моста между шинами MCA и комплексом ЦП и памяти. Поддерживаются 2 канала MCA со скоростью передачи 160 Мбайт/с каждый. Хотя поставляемая сегодня подсистема в/в базируется на технологии MCA, это не является принципиальным элементом архитектуры PowerScale. В настоящее время проводятся исследования возможностей реализации нескольких альтернативных шин ввода/вывода, например, PCI.

Рис. 4.5. Физическая реализация PowerScale

Платы памяти:

Каждая плата памяти состоит из четного числа банков. Максимальное число банков равно 16. Объем памяти на каждой плате может быть 64, 256 или 512 Мбайт.

Коммутатор данных (DCB) интегрирован в нескольких СБИС (4х16 бит) и функционально соединяет магистраль данных MPB_SysBus с подсистемой памяти, модулями ЦП и платой в/в. Ширина магистрали данных DCB на уровне массива памяти составляет 256 + 32 бит, а ширина магистрали данных для каждого порта ЦП и порта в/в равна 64 + 8 бит. Операции DCB управляются контроллером системной памяти (SMC) с помощью командной шины, обеспечивающей необходимую коммутацию устройств.

Семейство UNIX-серверов Escala

На российский рынок в настоящее время активно продвигаются UNIX-серверы семейства Escala - многопроцессорные системы с архитектурой PowerScale, построенные на базе микропроцессора PowerPC 601. Они предлагаются для работы в качестве нескольких типов серверов приложений: сервера транзакций (Transation Server) при использовании мониторов обработки транзакций подобных Tuxedo, сервера базы данных (Database Server) на основе таких известных систем как Oracle или Informix, а также управляющего сервера (System Management Server), обеспечивающего управление инфраструктурой предприятия и существенно упрощающего администрирование гетерогенными системами и сетями. Серверы Escala двоично совместимы с системами Bull DPX/20, а их архитектура разработана с учетом возможности применения новейших процессоров PowerPC 604 и 620.

Основные характеристики серверов Escala в зависимости от применяемого конструктива даны в таблице 4.1. Системы семейства Escala обеспечивают подключение следующих коммуникационных адаптеров: 8-, 16- и 128-входовых адаптеров асинхронных последовательных портов, 1- или 4-входовых адаптеров портов 2 Мбит/с X.25, а также адаптеров Token-Ring, Ethernet и FDDI.

Таблица 4.1

| МОДЕЛЬ Escala | M101 | M201D201 D401 R201 |

| Mini-Tower | DesksideRack-Mounted | |

| ЦП | ||

| Тип процессора | PowerPC 601 | |

| Тактовая частота (МГц) | 75 | 7575 75 75 |

| Число процессоров | 1/4 | 2/42/8 4/8 2/8 |

| Размер кэша второго уровня (Кб) | 512 | 5121024 1024 1024 |

| ПАМЯТЬ | ||

| Стандартный объем (Мб) | 32 | 6464 64 64 |

| Максимальный объем (Мб) | 512 | 5122048 2048 2048 |

| ВВОД/ВЫВОД | ||

| Тип шины | MCA | MCAMCA MCA MCA |

| Пропускная способность (Мб/с) | 160 | 160160 2x160 2x160 |

| Количество слотов | 6 | 615 15 16 |

| Количество посадочных мест | ||

| 3.5" | 4 | 47 7 7 |

| 5.25" | 2 | 23 3 3 |

| Емкость внутренней дисковой памяти Гб) | 1/18 | 1/182/36 4/99 - |

| Емкость внешней дисковой памяти (Гб) | 738 | 7381899 1899 2569 |

| Количество сетевых адаптеров | 1/4 | 1/41/12 1/12 1/13 |

| ПРОИЗВОДИТЕЛЬНОСТЬ (число процессоров 2/4) | ||

| SPECint92 | 77 | 7777 77 77 |

| SPECfp92 | 84 | 8484 84 84 |

| SPECrate_int92 | 3600/6789 | 3600/67893600/6789 - /6789 3600/6789 |

| SPECrate_fp92 | 3900/7520 | 3900/75203900/7520 - /7520 3900/7520 |

| Tpm-C | 750/1350 | 750/1350750/1350 750/1350 750/1350 |

Заключение

При разработке PowerScale Bull удалось создать архитектуру с достаточно высокими характеристиками производительности в расчете на удовлетворение нужд приложений пользователей сегодня и завтра. И обеспечивается это не только увеличением числа процессоров в системе, но и возможностью модернизации поколений процессоров PowerPC. Разработанная архитектура привлекательна как для разработчиков систем, так и пользователей, поскольку в ее основе лежит одна из главных процессорных архитектур в компьютерной промышленности - PowerPC.