Реферат: Цифровые системы управления связью

· число символов синхросигнала и частота повторения должны быть минимально возможными.

Схемы ПСС включают в себя блоки обнаружения синхросигналов (СС) на основе схем совпадения, счетчики обнаружения СС в данной временной позиции, счетчики-накопители по входу в синхронизм и выходу из синхронизма.

Работа системы сверхцикловой синхронизации, как и работа системы цикловой синхронизации, основана на передаче сверхциклового синхросигнала (СЦС) в одном из циклов сверхцикла. Принцип работы приемника СЦС аналогичен работе ПСС.

Рассмотрим структуру кадра передачи ЦСП ИКМ-30. Данный поток называется первичным цифровым потоком и организуется объединением 30-ти информационных ОЦК.

Канальные интервалы КИ1-КИ15, КИ17-КИ31 отведены под передачу информационных сигналов. КИ0 и КИ16 - под передачу служебной информации. Интервалы КИ0 в четных циклах предназначаются для передачи циклового синхросигнала (ЦСС), имеющего вид 0011011 и занимающего интервалы Р2 - Р8. В интервале Р1 всех циклов передается информация постоянно действующего канала передачи данных (ДИ). В нечетных циклах интервалы P3 и Р6 КИ0 используются для передачи информации о потере цикловой синхронизации (Авар. ЦС) и снижения остаточного затухания каналов до значения, при котором в них может возникнуть самовозбуждение (Ост. зат). Интервалы Р4, Р5, Р7 и Р8 являются свободными, их занимают единичными сигналами для улучшения работы выделителей тактовой частоты.

В интервале КИ16 нулевого цикла (Ц0) передается сверхцикловой синхросигнал вида 0000 (Р1 - Р4), а также сигнал о потере сверхцикловой синхронизации (Р6 - Авар. СЦС). Остальные три разрядных интервала свободны. В канальном интервале КИ16 остальных циклов (Ц1 - Ц15) передаются сигналы служебных каналов СК1 и СК2, причем в Ц1 передаются СК для 1-го и 16-го каналов ТЧ, в Ц2 - для 2-го и 17-го и т.д. Интервалы Р3, Р4, Р6 и Р7 свободны.

Принятая структура построения ЦСП ПЦИ реализуется посредством объединения и разделения типовых цифровых потоков. Сущность любого способа объединения заключается в том, что информация, содержащаяся в поступающих потоках, записывается в запоминающие устройства, а затем поочередно считывается в моменты, отводимые ей в объединенном потоке.

В наиболее общем случае объединения асинхронных (плезиохронных) потоков в объединенный поток помимо синхросигнала, указывающего порядок объединения, вводится служебная информация, обеспечивающая необходимое согласование скоростей объединяемых потоков.

Операции разделения потоков являются обратными операциям объединения: информация объединенного потока записывается в запоминающие устройства, соответствующие исходным потокам, затем считывается со скоростями, равными скоростям объединяемых потоков.

В большинстве случаев объединение потоков осуществляется посимвольно (побитно), т.е. считывание информации из запоминающих устройств при объединении происходит по разрядам: вначале считывается и передается разряд первого потока, затем - второго и т.д., после считывания разряда последнего из объединяемых потоков вновь считывается очередной разряд первого, т.е. цикл повторяется.

Возможно объединение и по группам символов. Например, в объединенном потоке можно вначале передать все символы, относящиеся к каналу или циклу передачи первого потока, затем - такую же группу символов второго и т.д. Объединение по группам символов требует увеличения объема памяти оперативных запоминающих устройств пропорционально числу объединяемых групп символов.

3.4.1. Элементы оборудования мультиплексирования сетей PDH

3.4.1.1. Амплитудно-импульсные модуляторы

Первым шагом в получении цифрового сигнала из непрерывного является его дискретизация. На первом этапе дискретизации формируется АИМ1 сигнал. Модулятором при этом выступает транзисторный ключ.

Схема представляет собой последовательный компенсированный ключ, который управляется импульсами от генераторного оборудования (ГО). Импульсы управления подаются на промежуток база-коллектор транзисторной сборки. Через R на базы транзисторов поступает дополнительное запирающее смещение, для более надежного запирания ключей.

Вторым шагом по формированию дискретного сигнала является АИМ2, задача которого расширить длину импульса на интервал дискретизации.

Выполняется по симметричной схеме. Когда ![]() и

и ![]() закрыты, на

закрыты, на ![]() обеспечивается мгновенное хранение значения данного канального интервала. За время хранения кодер успевает закодировать информацию. После этого под воздействием управляющих сигналов с ГО через формирователь импульсов ФИ ключи открываются, и

обеспечивается мгновенное хранение значения данного канального интервала. За время хранения кодер успевает закодировать информацию. После этого под воздействием управляющих сигналов с ГО через формирователь импульсов ФИ ключи открываются, и ![]() перезаряжается потенциалом нового уровня, соответствующего очередному значению канального интервала. Хранение на

перезаряжается потенциалом нового уровня, соответствующего очередному значению канального интервала. Хранение на ![]() обеспечивается тем, что входное сопротивление усилителей УС3 и УС4 более 1 МОм.

обеспечивается тем, что входное сопротивление усилителей УС3 и УС4 более 1 МОм.

3.4.1.2. Кодер с переменным шагом кодирования

Основной функцией кодера является выполнение операций квантования и кодирования АИМ сигналов, или иными словами, аналого-цифровой преобразование. Амплитуды АИМ сигналов кодируются в двоичном симметричном коде, при этом применяется принцип уравновешивания амплитуд тока кодируемых импульсов эталонными токами.

Используются кодеры взвешивающего типа с нелинейной характеристикой квантования. Нелинейное квантование заключается в изменении интервала квантования пропорционально изменению амплитуды входного сигнала, что позволяет достичь постоянства показателя: сигнал/искажение, появляющегося при ошибках квантования из-за резких изменений амплитуды сигнала, попадающих между отсчетами квантования.

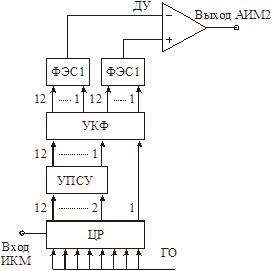

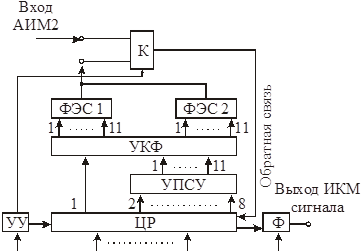

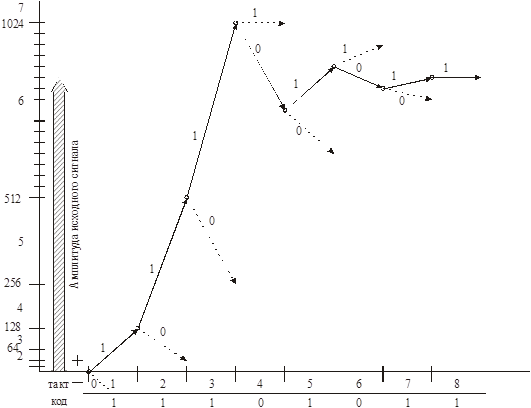

При кодировании применяется 8-ми разрядный код, где символ первого разряда несет информацию о полярности кодируемого сигнала, символы 2-го – 4-го разрядов соответствуют номеру сегмента, в пределах которого находится амплитуда сигнала. Символы остальных 4-ех разрядов соответствуют номеру интервала квантования в пределах данного сегмента. Для этого сегмента разделяется на 16 уровней с постоянным шагом квантования. Дифференциальный компаратор К определяет знак сигнала, сравнивая его амплитуду с амплитудами эталонных сигналов, формируемых ФЭС1 и ФЭС2 (положительный, отрицательный). В каждом формирователе эталонных сигналов 11 ключей, замыкание которых подает одну из эталонных условных единиц. Восьмиразрядный цифровой регистр ЦР с линией управления записывает и хранит информацию, поступающую от компаратора. Устройство преобразования сигналов управления УПСУ преобразовывает семиразрядный код (без знакового символа), поступающий с выводов ЦР в сигналы управления ключами ФЭС. Устройство коммутации УКФ пропускает эти сигналы к одному из ФЭС в зависимости от знакового символа. Формирователь выходного сигнала Ф, преобразует параллельный код в последовательный. Принцип работы кодирующей схемы поясняется диаграммой.

Если сигнал на входе компаратора положительный, то символом в 1-ом такте будет 1, а если отрицательный – 0. Поступая на УКФ, эти символы определяют, какой из ФЭС будет работать в последующих сети тактах. При воздействии на компаратор 2,3,4 управляющих импульсов от устройства управления (УУ) ищется сегмент характеристики компрессии, в пределах которого находится амплитуда. Поиск осуществляется методом поразрядного уравновешивания. При этом во втором такте на вход компаратора (2) подается средний из сети эталонных сигналов, соответствующий границам сегментов (128). В последующем последовательность смены этих эталонов зависит от результата сравнения эталонов с амплитудой кодируемого импульса. Если ![]() , то по цепи обратной связи во второй триггер ЦР передается 1, а в следующем 3-ем такте на второй вход подается средний из эталонов, значения которых больше 128 (а именно, 512). Если

, то по цепи обратной связи во второй триггер ЦР передается 1, а в следующем 3-ем такте на второй вход подается средний из эталонов, значения которых больше 128 (а именно, 512). Если ![]() , то по цепи обратной связи во второй триггер ЦР передается 0, а в следующем 3-ем такте на второй вход подается средний из эталонов, значения которых меньше 128 (а именно, 32).

, то по цепи обратной связи во второй триггер ЦР передается 0, а в следующем 3-ем такте на второй вход подается средний из эталонов, значения которых меньше 128 (а именно, 32).

Аналогично в 3-ем и 4-ом тактах, но уже в сегментах в соответствие с выбором во втором такте. Таким образом, к концу 4-го такта определяется эталонный сигнал, соответствующий нижней границе сегмента, в котором находится амплитуда, а во 2-ом – 4-ом триггерах ЦР будут записан двоичный номер сегмента.

Далее определяется положение амплитуды внутри выбранного сегмента. Для этого на протяжении 5 – 8 тактов последовательно осуществляется сравнение с эталонами, разделяющими выбранный сегмент. При этом поиск также начинается от середины сегмента, а последующий выбор эталонов зависит от того, в какой части сегмента оказалась амплитуда кодируемого сигнала.

3.4.1.3. Декодер с переменным шагом квантования

Декодеры предназначены для преобразования поступающих кодовых комбинаций на основе эталонных сигналов в сигнал АИМ2. Структурная схема декодера с переменным шагом квантования: