Реферат: Універсальні мікропроцесори, застосовувані в ММПС. Мікропроцесори з архітектурою Itanium (IA-64)

FR0-FR127 – регістри формату плаваючої коми, місткістю 82 біт, з яких FR0, FR1 – доступні тільки для читання, FR2- FR33 – 32 глобальні регістри, інші 96 що обертаються регістра (циклічних);

PR0-PR63 - предикативні регістри, з яких 16 статичних, інші 48 що обертаються. Предикативні регістри служать для ухвалення рішення про виконання команди. Команда виконується, якщо відповідний їй предикативний регістр рівний 1.Если предикативний регістр не заданий явно, за умовчанням приймається регістр PR0, значення якого завжди рівно 1;

BR0-BR7 – регістри галужень, в яких зберігаються призначені адреси галужень команд;

AR0-AR127 –прикладные регістри, які використовуються для допоміжних функцій.

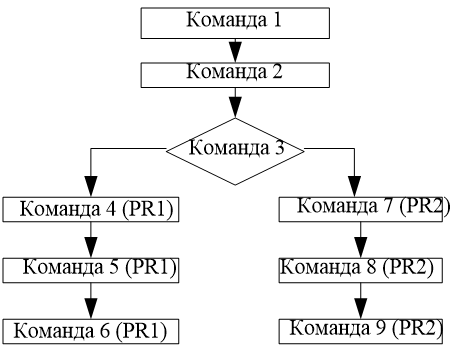

Компілятор IA-64 використовує технологію відзначених галужень. Ця технологія припускає, що команди, що належать різним гілкам алгоритму, позначаються різними значеннями в полі предиката команди. Формування зв'язок команд здійснюється в незалежності від значень предиката. Тим самим забезпечується можливість одночасного виконання команд, що належать різним гілкам алгоритму. В процесі виконання програми, після результати команд із значенням предиката, відповідного даній гілці. Проте не всі гілки наголошуються компілятором для паралельного виконання, відмітка здійснюється для коротких альтернативних гілок і якщо гілка не наголошується, то передбачається мікропроцесором в процесі виконання програми.

Принцип прогнозу виконуваних інструкцій приведений на мал.4

|

Малюнок 4. Принцип прогнозу виконуваних інструкцій

Всі команди гілки 1 мають посилання на регістр прогнозів (предикативний) PR1, гілки 2 – PR2. Обчисливши умову переходу процесор відкидає помилковий результат обчислень. В результаті процесор може переупорядкувати команди відповідним чином.

| Команда 1 | Команда 2 | Команда 3 |

| Команда 4 | Команда 7 | Команда 5 |

| Команда 8 | Команда 6 | Команда 9 |

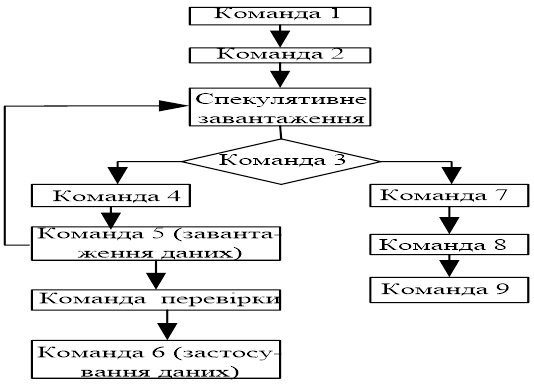

Наступна особливість архітектури IA-64 - попереднє (спекулятивна) завантаження даних в кеш-пам'ять. Єство спекулятивного завантаження – рознесення в часі команд завантаження даних з пам'яті і команд їх використовуючи. Функції компілятора в цьому випадку – аналіз початкового тексту програми і завантаження команд перевірки на доступність. Схема спекулятивного завантаження приведена на мал. 5.

|

Малюнок 5. Схема спекулятивно го завантаження

Компілятор по можливості вставляє команди спекулятивного завантаження і перевірки. Якщо у разі спекулятивного завантаження виникає особливий випадок, процесор не поспішає повідомляти про це програмне забезпечення.

Організація пам'яті також унікальна, тобто відмінна від всіх попередніх реалізацій мікропроцесорів фірми INTEL. Місткість адресного простору 264 і воно лінійне, немає ні сегментації ні сторінкової адресації. В даному адресному просторі немає конкретно закріплених фізичних адрес, тобто весь діапазон адресації програмно доступний. Для забезпечення сумісності з раніше розробленими 32-додатками в IA-64 передбачається використовування двох режимів VLIW і CISC. Перемикання здійснюється програмно за допомогою спеціальної команди.

Реалізація циклів також відмінна від класичної і більш схожа з архітектурою RISC процесорів. Цикл ділиться на три фази – пролог, ядро і епілог. Апаратна підтримка на кожній з фаз – механізм ²обертання² регістрів, спеціальні команди, спеціальні прикладні регістри ( лічильник циклів і лічильник епілогів). В мікропроцесорі не використовується динамічне перейменування регістрів, натомість – схема циклічної заміни використаних регістрів (обертання регістрів). При цьому набір що використовуються в циклі регістрів розглядається як фрейм, що відображається на регістровий файл, починаючи з деякою позицією – бази фрейма. При переході на наступну ітерацію циклу змінюється база фрейма – збільшується (зменшується) на величину рівну кількості регістрів у фреймі.

ЛІТЕРАТУРА

1. Б.В.Шевкопляс Микропроцессорные структуры. Инженерные решения М.: Радио и связь, 1990

2. В.Шевкопляс Микропроцессорные структуры. Инженерные решения. Дополнение первое.М.: Радио и связь, 1993

3.М.Гук Аппаратные средства IBMPC С.Петербург ²Питер² 2000

4. В.Корнеев, А.КиселевСовременные микропроцессорыСанкт-Петербург,²БХВ–Петербург² 2003

5. Локазюк В.М. и дрМикропроцессоры и микроЭВМ в производственных системахКиев Издательский центр ² Академия ² 2002

6. В.В.Сташин, А. В. Урусов, О.Ф. МологонцеваПроектирование цифровых устройств на однокристальных микроконтроллерахЛ. Энергоатомиздат

7. Под ред.А.Д.Викторова Руководство пользователя по сигнальным микропроцессорам семейства ADSP-2100 Санкт- Петербургский государственный электротехнический университет. Санкт- Петербург 1997

8. М.Предко Руководство по микроконтроллерам в 2-х томах М: Постмаркет, 2001