Учебное пособие: Адресное пространство. Подсистемы ввода-вывода

В качестве операндов кроме данных в АЛУ поступают и адреса, следовательно, разрядность ЦП прямо определяет размер адресного пространства.

Архитектуры ЦП

Скалярная.

ЦП делится на две секции, каждая из которых независимо тактируется одним тактовым генератором.

Идея: АЛУ не должно простаивать, пока идет выборка команды из памяти.

Выборка инструкции происходит параллельно с работой АЛУ. Для этого используется конвейер.

Суперскалярная.

Несколько АЛУ и каждое занимается своим делом. Добавляется АЛУ для вычисления адресов. Несколько команд могут выполняться одновременно. Возникает проблема, когда команда, стоящая в памяти дальше, выполняется быстрее. Выход – механизм замещения регистров: используются копии регистров для хранения результатов.

Принцип параллельности команд – независимость операндов, т.е. если у команд есть общий операнд – они не параллельны. Если в инструкциях операнды в памяти, то трудно проверить, пересекаются ли они – процессор считает такие команды не параллельными. Процессор оперирует относительными адресами в адресном пространстве процесса, которые дал компилятор и линковщик. Два адреса могут указывать на одно место в физической памяти и два одинаковых адреса – на разные участки физической памяти.

Архитектура RISC.

Запрещает использовать методы адресации во всех инструкциях, кроме load и store. Все мнемонические команды остаются (они необходимы всем ЦП).

addR0,R1 команды почти одинаковы с точки

subR0,R1 зрения внутренней топологии

addR0,R1 эти сильно

addR0,(R1) отличаются

Запретив команды addR0,(R1) существенно меняем набор команд.

Таким образом, можно максимально сгруппировать команды загрузки из/в память. Еще надо побольше регистров (лучше несколько десятков).

Рост быстродействия RISC колоссален, по сравнению с CISC (если еще использовать кэш для ОП и сгруппировать обращения к ОП вместе).

Адресное пространство

Существует два типа адресных пространств:

- Логическое АП – этими адресами оперирует ЦП (разрядность ЦП)

- Физическое АП – этот адрес выставляется на шину.

В общем случае ЛА и ФА – разные.

ЦП не может сгенерировать адрес, выходящий за пределы его разрядности. Для памяти нужен ФА большой разрядности.

Возникает две проблемы:

1. Сделать физическую память разрядности больше разрядности ЦП.

2. Если увеличить разрядность ФА, тогда не хватит физической памяти, что делать? (Например, 32-разрядный процессор позволяет каждому процессу иметь ЛАП 4Гб, но где взять столько физической памяти)

Пусть ЛАП < ФАП.

|

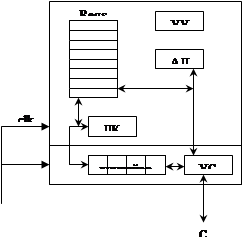

Тогда нужен отдельный базовый регистр для кода – CS. Следовательно, ЦП должен выдавать Устройству Сопряжения с Шиной какой-то признак вместе с операцией, чтобы УСШ знало, какой базовый регистр использовать.

Все операции работы с памятью используют CS, если выбирается код, и DS, если выбираются данные.

|