Дипломная работа: Створення мікропроцесорної системи для багатоканального інформаційного табло

- універсальний асинхронний адаптер;

- байт орієнтований двох провідний послідовний інтерфейс;

- 6/8 канальний АЦП з точністю до 8 і 10 двійкових розрядів;

- сторожовий таймер;

- послідовний порт SPI;

- розширені режими управління енергоспоживання.

Основні елементи архітектури мікроконтролера ATmega8.

Ядро мікроконтролера, що зображене на рисунку 5, виконує команди програми.

Рисунок 5 Блок – схема ядра AVR

Ядро включає елементи гарвардської архітектури з незалежними шинами, тому вибірка інструкцій проводиться незалежно від операцій в арифметично логічному пристрої (АЛП).

Старші 6 8-ми бітових регістрів утворюють 3 регістрові пари, які використовуються для адресації пам'яті - X,Y,Z.

АЛП проводить арифметико-логічні операції між регістрами (без обмежень) і регістром і константою. Кожна арифметико-логічна операція встановлює прапори в регістрі прапора (рис. 6).

Рисунок 6 Регістр прапора контролера

I - прапор дозволу переривання;

T - прапор-хранитель біта - встановлюється і аналізується тільки спецінструкціями;

H - прапор додаткового перенесення з 3-го розряду в 4-й;

S - прапор знаку результату;

V - прапор переповнювання;

N - прапор негативного результату операції;

Z - прапор нуля;

С - прапор перенесення.

В АЛП підтримується апаратний стек у внутрішній статичною пам'яттю.

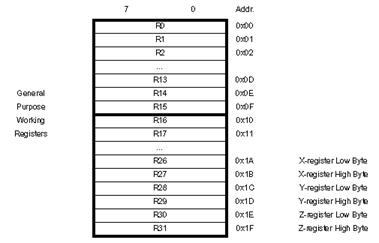

Структура регістрового файлу показана на рисунку 7.

Рисунок 7 Структура регістрового файлу AVR

На рисунку 7 видно, що 6 старших регістрів утворюють регістрові пари - індексні регістри. Ядро процесора за допомогою цих регістрів допускають автоінкрементну, атодекрементну адресацію і адресацію з малим зсувом.

Ядро процесора ATmega працює в декілька таймерів 0-му та 1-му.

0-й таймер загального призначення має 8-бітовий лічильник з 10-бітовим додатковим дільником частоти. Таймер може генерувати переривання по переповнюванню, або по досягненню значення.

1-й таймер має 16-бітовий лічильник. Він може бути використаний для генерації сигналів із змінною шин (широко імпульсні модуляції), генерації частоти і визначення часу надходження зовнішніх подій.