Курсовая работа: Моделирование процессора (операционного и управляющего автоматов) для выполнения набора машинных команд

);

end RA;

architecture RA of RA is

signal reg: std_logic_vector (7 downto 0):= «00000000»;

begin

process (CLK, RAIn)

begin

DOut<=reg after 3 ns;

if CLK='0' and CLK'event and RAIn='1' then

reg<=DIn;

end if;

end process;

end RA;

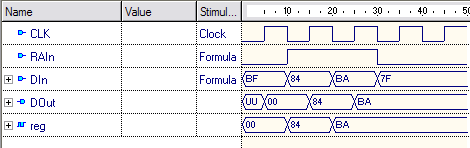

Временная диаграмма работы регистра-аккумулятора RA:

Описаниеузлапамяти Memory:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_signed.all;

entity Memory is

port (Adr: in std_logic_vector (5 downto 0);

RD: in std_logic;

MrOut: out std_logic;

InstrCom: out std_logic_vector (0 to 27));

end Memory;

architecture Memory of Memory is

type MemoryType is array (0 to 59) of std_logic_vector (0 to 27);

signal Memory: MemoryType;

begin