Курсовая работа: Преобразователь кода (ПК)

2.1. Составление таблицы истинности ПК.

2.2. Написание булевых функций ПК.

2.3. Минимизация булевых функций ПК.

2.4. Преобразование булевых функций ПК к выбранному базису.

2.5. Составление структурной схемы ПК.

2.6. Обоснованный выбор элементной базы, представление ИМС.

2.7. Составление электрической схемы в соответствии с ЕСКД.

2.8. Расчеты энергопотребления и быстродействия устройства.

2.9. Предусмотреть вход стробирования низким уровнем CS ( IE ).

3. Заключение. Выводы о соответствии ТЗ на проектирование и достигнутых результатов.

4. Выполнить моделирование разработанного ПК, используя, например, популярный пакет ElectronicsWorkbench (версии 5.12 или ниже), либо доступный Вам на сайте кафедры «Промышленная электроника» ТУСУР пакет ASIMEC (русифицированный и более мощный по используемым математическим средствам моделирующий пакет с отечественными компонентами и с возможностью их редактирования и пополнения библиотеки).

5. Рекомендуемое задание - выполнить трассировку печатной платы для электрической схемы ПК, используя доступные Вам многочисленные (например, ACCELTechP-CAD 2000 (с), CamCadGraphicv.3.8, SpectraAutoRouter 7.0.2, ExpeditionPCB 2000 или другие) прикладные программы.

Выполнение пунктов 4 и 5 не является обязательным, но желательным, т.к. показывает стремление обучающегося не ограничивать себя минимальными знаниями, а работать творчески и в полную силу.

Приложения:

А. Структурная схема ПК.

Б. Электрическая схема ПК.

В. Поразрядные временные диаграммы для входов и выходов ПК.

Г. Трассировка печатной платы для электрической схемы ПК (при выполнении п.4).

2. Этапы проектирования ПК

| |

|

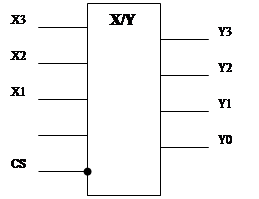

Рис.1. ИМС ПК

2.1. Составления таблицы истинности ПК.

| Входной код Х вх | Выходной код Y вых | |||||||

| G4 | 2421 | |||||||

| N | X3 | X2 | X1 | X0 | Y3 | Y2 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 8 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 9 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

2.2. Написание булевых функций ПК.

Булевы функции семи выходов ПК (для каждого из сегментов) записываются в дизъюнктивной нормальной форме и приведены ниже:

![]() ;

;

![]() ;

;

![]()

![]()

Данная система булевых функций не является минимальной и привела бы к существенной избыточности структуры ПК при реализации на ее основе. Поэтому следующим логическим шагом процедуры проектирования является минимизация булевых функций ПК.

Для минимизации булевых функций используем правила алгебры Буля и процедуру Карт Карно: