Курсовая работа: Преобразователь кодов Манчестер-2

Одним из ведущих направлений развития человеческого общества является информатизация – всё большее внедрение компьютерных технологий в различные сферы человеческой деятельности, с целью повысить эффективность его труда. Одним из направлений этого движения является создание различных сетей передачи данных, и других систем нуждающихся в обмене данными. Эти данные передаются посредством различных способов физического и логического кодирования. Одним из наиболее распространенных типов физического кодирования информации для передачи на средние и большие дистанции является код Манчестер-2.

В Манчестерском коде для кодирования единиц и нулей используется перепад сигнала, то есть фронт импульса. Каждый такт делится на две части. Так как сигнал изменяется по большей мере один раз за такт передачи одного бита данных, то манчестерский код обладает хорошими самосинхронизирующими свойствами. У него нет постоянной составляющей, а основная гармоника в худшем случае (при передаче последовательностей нулей и единиц) имеет частоту N Гц, а в лучшем (при передаче чередующихся единиц и нулей) – N/2 Гц. Поскольку отсутствие высокого или низкого уровня в течение всего интервала бита недопустимо, появление таких ситуаций может свидетельствовать об ошибке.

Эти свойства и наличие самосинхронизации, исключающей возникновение фазовых сдвигов между информационными и синхронизирующими последовательностями, определили использование кода «Манчестер-2» как основного для каналов последовательной передачи в протоколе Ethernet, бортовых САУ и целом ряде коммерческих систем.

Проектируемый кодер преобразует последовательный двоичный код (NRZ - используется для передачи данных между блоками различных вычислительных систем, в виду своей простоты) в Манчестер-2, что позволяет производить надежный обмен данными между удалёнными устройствами.

1. Выбор и обоснование направления проектирования

В результате обзора широкого спектра литературы и интернет источников, были найдены аналоги устройства, которые выполняют схожие задачи. Практически все устройства схожи с техническим заданием, но не до конца удовлетворяют его требованиям. Проблемой также стало отсутствие, в большинстве случаев, детальной информации по найденным аналогам, позволяющей использовать их проектировании необходимого устройства.

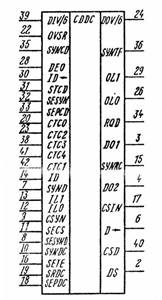

Транзитивный метод физического кодирования сигнала Манчестер-2 (Manchestercode, также за рубежом Phase Encoding или PE) на данный момент один из самых распространенных в различных САУ и ЛВС. Так, например, Манчестер-2 применятся в стандартах сетевых протоколов Ethernet, TokenRing, MIL-STD-1553B(ГОСТ. 52070-2003), MIL-STD-1760 и многих других, применяемых в различных областях от построения коммерческих локальных сетей, до бортовых САУ в авиации и судостроении. Такое широкое применение Манчестерского кодирования обуславливает довольно большое количество электронных кодирующих устройств, в частности, на западе выпускают ряд КМДП монолитных кодеров/декодеров Манчестера(CMOS Manchester Encoder/Decoder) : серий 3D7501, ACT-15530, а также HI-15530, HD-15530, HD-15531, СТ-10894 и другие. В России разнообразие не столь велико, удалось найти информацию лишь о КМДП ИС К588ВГ3 и К588ВГ6, созданных ещё в конце 80-х годов. Ниже, на рисунке 1.1, для ознакомления показаны условное графическое представление К588ВГ3.

Рисунок 1.1 – Условные графические представления К588ВГ3

Но ни одна из названных БИС не удовлетворяет условиям технического задания - все имеют недостаточный диапазон тактовых частот: для микросхем серии 3D7501, предназначенных для работы в сетевых картах, он доходит до 50 МГц, а для ACT15530, HI-15530, К588ВГ3 и К588ВГ6 предназначенных для работы в сетях протокола MIL-STD-1553, всего лишь до 1,25 МГц. Остальные существенные параметры К588ВГ3 приведены в таблице 1.

Кроме того, практически все упомянутые ИС кодируют биполярный Манчестер-2, проектируемое же устройство, согласно техническому заданию кодирует униполярную разновидность Манчестера-2.

Таблица 1 – Электрические параметры К588ВГ3, КР588ВГ3

| Номинальное напряжение питания | 5 В ± 5% |

| Выходное напряжение низкого уровня | 0,4 В |

| Выходное напряжение высокого уровня | (Uп – 0,4) В |

| Ток потребления | ≤ 0,1 мА |

| Время задержки распространения сигнала (от входа 10 до выхода 36) | ≤ 80 нс |

| Максимальная емкость нагрузки | 100 пФ |

| Частота работы канала | 1,25 МГц |

Однако причиной невысокой, по современным меркам, частоты работы канала является не принципиальный изъян используемых в этих БИС принципов кодирования, а не достаточная скорость работы элементной базы. Таким образом, используя более быстрые компоненты, можно достичь необходимой тактовой частоты без изменения схемы работы этих устройств. В этом ключе, их несомненно можно рассматривать как аналоги при разработке курсового проекта. По зарубежным ИС не удалось найти электронных принципиальных и элементных схем. Поэтому проанализируем отечественную БИС К588ВГ3, которая, в целом, идентична HI-15530 (не исключаю возможности, что К588ВГ3 была напрямую скопирована с зарубежных образцов, в виду небольшого отставания СССР в области компьютерных технологий в те годы и внедрения в производство стандарта сетевых протоколов ГОСТ 26765.52-87 (MIL-STD-1553)).

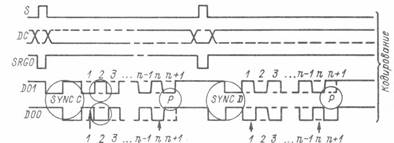

Рисунок 1.2 – Структура и принципиальная временная диаграмма работы кодера К588ВГ3

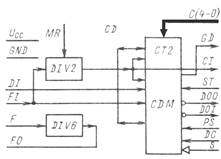

В состав кодера (CD) БИС КДК входят:

DIV 6 — делитель на 6, используемый для получения из частоты синхронизации декодера (12f) частоты синхронизации кодера (2f);

DIV 2 — делитель на 2, используемый для получения из частоты синхронизации кодера 2f частоты приема данных в кодер (1f);

CDM — кодер манчестерского кода;

СТ2 — счетчик числа передаваемых в слове битов.

Для нас наиболее важен кодер, находящийся в блоке CDM, остальные части ИС К588ВГ3 выполняют действия, в которых, согласно техническому заданию, нет необходимости.

В таблице 2 описаны выводы БИС кодера.

Временная диаграмма, поясняющая общие принципы использования БИС КДК, приведена на рисунке 1.3. При передаче строом SRGO производится запись слов, подлежащих кодированию, во внешний параллельно-последовательный регистр, данные из которого в последовательном коде поступают на вход DI по синхроимпульсам С1 . При приеме информации из МК стробом SRGI может выбираться внешний последовательно-параллельный регистр, используемый для накопления декодированных данных, поступающих с выхода DO по синхроимпульсам СО в последовательном коде. Формирование сигналов SRGI и SRGO производится внешней схемой на основе сигналов TD и GD (выходы синхронизации приема/передачи слова).

При передаче кодер в зависимости от уровня сигнала на входе DC автоматически вырабатывает нужный синхроимпульс SYNC С или SYNC D и вставляет бит четности (Р). Согласование работы кодера с оконечным устройством осуществляется сигналами запуска передачи S, запрета на выдачу очередного слова ST и строба выдачи слов CD .

Таблица 2 –Описание выводов БИС кодера К588ВГ3

Обознач. | Номер контакта | Назначение вывода |

| DI0, DI1 | 12,13 | Униполярные фазоманипулированные инверсные входы «нуля» и «единицы» декодера (прямые) |

| DO0, DO1 | 26, 29 | Униполярные фазоманипулированные выходы «нуля» и «единицы» кодера (инверсные) |

| FO | 24 | Выход частоты синхронизации кодера (2 МГц) |

| С I | 36 | Выход тактовой частоты приема кодера (1 МГц) |

| MR | 22 | Вход общего сброса КДК |

| DC | 32 | Вход задания типа генерируемого синхроимпульса (SYNCD или SYNC С) |

| S | 34 | Вход запуска кодера |

| ST | 28 | Вход разрешения выдачи биполярного кода |

| PS | 33 | Вход задания полярности контрольного бита шифратора кодера |

| F | 39 | Вход делителя на шесть (12 МГц) |

Рассмотрим организацию непосредственно кодера Манчестерского кода, обозначенного на схеме аббревиатурой CDM. На рисунке 4 представлена его функциональная схема вместе с другими блоками, работающими в кодере К588ВГ.

Перед тем как попасть непосредственно на шифратор информация проходит через счётчик битов СТ2, (показан на рисунке 3), который сравнивает код на входах С0 – С4 с числом тактов, в течение которого принимается слово, причёмподсчет битов ведется по модулю п +4 (n – число битов), так как слово включает синхроимпульс и бит четности. Также перед шифратором находятся счетчики/делители, организованные по обычной схеме и реализуемые на основе одного (Т6) и трех ( T 7— T 9) триггеров (соответственно DIV 2 и DIV 6 – показан только на рисунке 3).

Схема шифратора (построена на триггерах Т10—Т16) подстраивает фазу передаваемых сигналов к частоте 2f, принимаемой по входу FI , и синхрочастотой С I стробирует ввод данных с входа DI ; код «Манчестер-2» выдается на выходы DO 0, DO 1. Сигнал ST заведен на выходные элементы, стробирующие выдачу информации. Триггер Т10 включен по схеме счетчика и накапливает сумму передаваемого кода по четности или нечетности в зависимости от полярности сигнала PS .

Несложно заметить, что данная схема, как и другие найденные аналоги, избыточна и чрезмерно сложна, по сравнению с устройством, которое необходимо разработать по техническому заданию.