Курсовая работа: Программно-аппаратный комплекс для тестирования интегральных микросхем 155 серии

Работа тестера проходит следующим образом:

В начальный момент времени питание тестера отключено, соответственно на выходе контроллера какие-либо сигналы отсутствуют. В момент включения питания тестера, подается питание на контроллер, который переходит в состояние ожидания команды на тестирование. Выполнение данной команды осуществляется нажатием кнопки "тест" - SB2. Питание тестируемой микросхемы в это время отключено. Далее осуществляется выбор тестируемой ИМС. Номер тестируемой микросхемы задается переключателями S1-S8 в двоичном коде. После того как требуемый тип микросхемы выбран, а тестируемая микросхема установлена на контактной площадке ХS1.1 - XS1.2, можно нажимать кнопку "тест". При нажатии кнопки тест, микропроцессором считывается номер микросхемы, и подается питание на тестируемую микросхему. Далее контроллер выполняет подпрограммы тестирования микросхемы. В порт микроконтроллера, подключенный к входам тестируемой микросхемы записываются комбинации сигналов, с заранее известными верными состояниями выходных сигналов, и считываются значения выходных сигналов, которые потом сравниваются с эталонными. Микросхема исправна при совпадении сигналов, считанных с выходов тестируемой микросхемы и эталонных сигналов. Тестером выдается сигнал - "Исправен". При не совпадении сигналов на выходе и ожидаемых (эталонных) сигналов выдается сигнал "Не исправен", следовательно, ИМС бракуется. После вывода результата питание с тестируемой микросхемы снимается до поступления следующей команды на тестирование.

Стоит отметить, что для работы на данном тестере, оператор должен уметь задать номер требуемой ИМС в двоичной системе счисления и считать его с индикаторов VD5, VD6 в шестнадцатеричной.

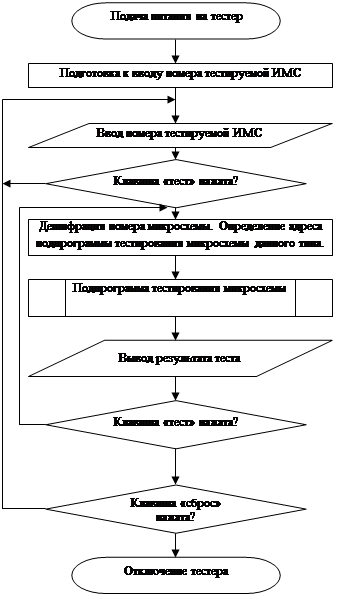

3. Разработка обобщенной блок-схемы алгоритма работы контроллера

По описанному режиму работы тестера составляется блок-схема алгоритма работы контроллера, которая изображена на рис 3.1 Контроллер начинает работать с подачи на него питания. После подачи питания он проводит самотестирование и переходит в состояние ввода номера тестируемой микросхемы, после чего переходит в режим ожидания нажатия кнопки "тест", SB2.

|

Рис.3.1. Обобщенная блок схема алгоритма работы тестера

Как только срабатывает кнопка "тест", микроконтроллер, по заданной комбинации ключей S1-S8 производит дешифрацию номера микросхемы. В соответствии с номером ИМС определяется адрес подпрограммы и ей передается управление для тестирования заданного типа микросхемы. Выполняется тестирование микросхемы. Потом происходит вывод результатов тестирования ИМС. Далее контроллер ждет действий оператора. При нажатии клавиши SB2 ("тест"), производится повторное тестирование установленной микросхемы. При нажатии клавиши SB1 ("Сброс"), контроллер произведет самотестирование и будет ожидать ввода нового типа микросхемы.

При необходимости завершить работу с тестером, питание тестера отключается.

4. Разработка интерфейса программно-аппаратного комплекса

Аппаратная часть интерфейса тестера для взаимодействия микроконтроллера и тестируемой микросхемы будет выглядеть следующим образом. Микроконтроллер имеет четыре двунаправленных 8-ми разрядных порта ввода/вывода. Порт Р3 также является линиями управления внешними устройствами (Р3.0, Р3.3), а также его линии задействованы для индикации результата тестирования (Р3.4 - Р3.6). В порт Р0 (Р0.0 - Р0.7) подаются тестовые комбинации сигналов на тестируемую ИМС. В порт Р2 (Р2.0 - Р2.1) заводятся результаты опроса выходов ИМС. Комбинации тестовых сигналов представлены в табл.4.1

Таблица 4.1 Тестовые сигналы для ИМС К155ЛА1

| № теста | Тестовые сигналы | ||||||||

| Обозначение битов порта Р1 | Байт P0 | ||||||||

| Р0.7 | Р0.6 | Р0.5 | Р0.4 | Р0.3 | Р0.2 | Р0.1 | Р0.0 | ||

| Функциональные обозначение выводов тестируемой ИМС | |||||||||

| X8 | X7 | X6 | X5 | X4 | X3 | X2 | X1 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00Н |

| 2 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 88Н |

| 3 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 44Н |

| 4 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | ССH |

| 5 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 22Н |

| 6 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 55Н |

| 7 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 66Н |

| 8 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | ЕЕH |

| 9 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 11Н |

| 10 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 99Н |

| 11 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55Н |

| 12 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | DDH |

| 13 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33Н |

| 14 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | ВВН |

| 15 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | ЕЕН |

| 16 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | FFH |

Порт Р2, биты Р2.0 - Р2.3, подключается к выходным выводам тестируемой МС. Возможные комбинации правильных ответных сигналов сведем в табл.4.2

Таблица 4.2 Ответные сигналы ИМС К155ЛА1

| № теста | Ответные сигналы | ||

| Обозначение битов порта Р0 | Байт P2 | ||

| Р2.1 | Р2.0 | ||

| Функциональные обозначение выводов тестируемой ИМС | |||

| Y2 | Y1 | ||

| 1 | 1 | 1 | 03Н |

| 2 | 0 | 0 | 00Н |

Биты порта P3 используемые для вывода на элементы индикации описаны в табл.4.3

Таблица 4.3

Назначение линий порта P3.

| Обозначение | Назначение |

| P3.4 | Сигнал для подачи напряжения на индикатор "Исправен" |

| P3.5 | Сигнал для подачи напряжения на индикатор "НЕ исправен" |

| P3.6. | Сигнал для подачи напряжения на индикатор "Готов" |

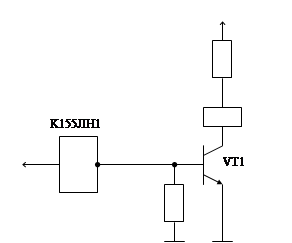

Порт P3 используется для управления подачей питания на испытуемую микросхему через исполнительные элементы (логический элемент с большим выходным током, транзисторный ключ и реле, рис.4.1) с линии P3.0 и отслеживается включение переключателя "тест" через линию Р3.3 - прерывание от внешнего устройства.

Программная часть интерфейса заключается:

По приходу сигнала прерывания определяется тип тестируемой МС, считывается значение, выставленное переключателями S1-S8 на линиях порта P1 (Р1.0 - Р1.7). Дешифрируется тип МС, и управление передается подпрограмме, которая производит тестирование МС данного типа. Подпрограммой тестирования, выставляются тестовые комбинации сигналов в порт P0 (биты Р0.0 - Р0.7), потом производится считывание ответа МС из порта P2 (биты Р2.0 - Р2.1), и оценивается его работоспособность. В зависимости от результата сравнения ожидаемого значения и ответа микросхемы, загорается либо зеленый светодиод - "исправен", либо красный - "не исправен" (порт Р3, биты Р3.4 - Р3.5 соответственно).

Схема управления для подачи питающего напряжения на испытуемую микросхему

|

???.4.1

5. написание подпрограммы тестирования интегральной микросхемы К155ЛА1

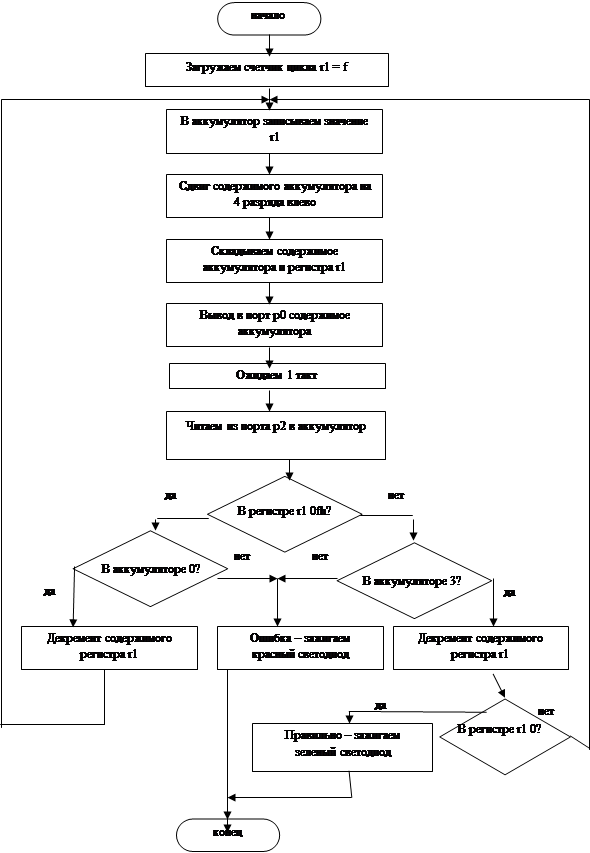

Задачей подпрограммы тестирования микросхемы К155ЛА1 является поочередная подача на входы тестируемой МС всех комбинаций таблицы истинности для данной микросхемы таблица 4.1 Блок-схема, по которой подпрограмма тестирования перебирает все необходимые для тестирования варианты и проверяет на соответствие с эталонными значениями (табл.4.2) приведена на рис.5.1.

После установки МС на контактной площадке и выбора ее типа, работа программы происходит в следующем порядке:

Подачу тестовой комбинации сигналов на вход ИМС осуществляем путем записи числа в порт P0. Затем программа считывает данные из порта P2, затем обнуляем старший полубайт, т.к там записана служебная информация, не относящаяся к ответу ИМС. Затем производим логическое сложение с заранее известным верным, но инвертированным, сигналом ответа. (в случае работоспособности ИМС должна получиться сумма равной 111111112 ). Затем полученную сумму инкриминируем. Если появился бит переноса, то продолжаем тестирование ИМС подачей следующие тестовой комбинации из таблицы истинности, табл.4.1 Если бит переноса при сложении равен нулю, то заканчиваем программу, подавая сигнал на индикатор неисправности микросхемы; После перебора всей таблицы истинности, в случае установления бита переноса в единицу, заканчиваем программу, подавая сигнал на индикатор исправности микросхемы; далее контроллер ожидает следующего нажатия кнопки "тест" или "сброс".

По описанию и блок схеме составили подпрограмму тестирования ИМС К155ЛА1, табл.6.

Алгоритм тестирования ИМС К155ЛА1

Рис.5.1.

Подпрограмма проверки ЛА1.

la1: movr1,#0fh; загрузка счетчика цикла

cmp_st: mova,r1; в аккумулятор записываем значение регистра r1

rla; данные в

rla; аккумуляторе сдвигаем на

rl a; 4 разряда