Курсовая работа: Разработка цифрового таймера

1

1

0

0

0

0

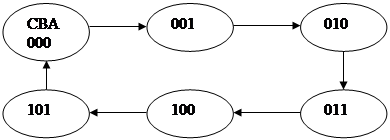

Асинхронный счётчик с автоматическим сбросом (деление на пять)

В счётчике с автоматическим сбросом используется несколько иные методы счёта. Счётчик по модулю 5 производит счёт от 0 до 5, причём логический сигнал, представляющий число 5, используется для очистки всех триггеров счётчика. На рис.5. показана диаграмма состояний счётчика с автоматическим сбросом по модулю 5.

Счетчик остаётся в каждом из первых пяти состояний в течение интервала времени, равного периоду тактового сигнала. Но при записи шестого состояния (101) элемент И-НЕ вырабатывает сигнал сбросаr =(Т1 Т1' Т3)' . Как это делается, показано на рис.2.2. На рис.6.изображенывременные диаграммы, характеризующие работу схемы счётчика.

Рис.6

![]() S5

S5

Время сброса для разных триггеров, образующих счётчик, бывает разным.

![]()

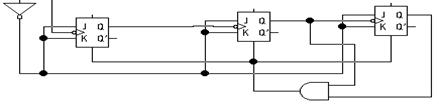

Рис. 7.

Рис. 7.

Например, в следующей схеме рис. 7. триггер Р1 может сбрасываться быстрее, чем триггер Р3 .

В предыдущей схеме (Рис.7.) на выходе элемента 3 появляется логическая <<1>>, когда счётчик переходит в состояние S5 . Это означает, что на выходе Q появляется логический <<0>>.Следовательно, сигнал Q'=r используется для очистки триггеров счётчика. Схема запирания остаётся в состоянии Q=1 до тех пор, пока не появится шестой тактовый импульс. Этот импульс сбрасывает триггер, и значение Q'=r становится равным логической <<1>>. Цикл работы схемы запирания завершается, когда значение AB'C становится равным логической <<1>>.

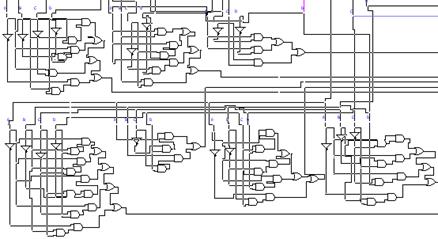

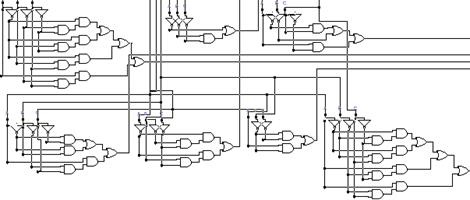

Рис. 8.

Дешифратор, с коэффициентом пересчёта 10 (включая 0), схема которого показана на Рис 8., имеет четыре входа и один выход и выполняет следующую функцию: каждому входному слову (m-разрядному коду), соответствует сигнал 1 (или в других случаях – сигнал 0) на выходе. Таким образом, для построения дешифратора можно использовать элементы И, на входы которых подаются входные сигналы и их инверсные значения.

Дешифратор преобразует поступающий на него двоичный код в десятичный.

Аналогично строится дешифратор с коэффициентом пересчёта 6 (включая 0)Рис.10.

Рис.10.

С выходов дешифратора десятичные импульсы поступают на индикатор Рис.11.

Принцип синтеза цифр в семисегментном коде иллюстрируется Рис.11. На Рис.11. приведена семисегментная матрица.

Рис. 11

Её отдельные сегменты, соответствующие определённым выходам дешифраторов, D1-D7, обозначены последовательностью прописных букв латинского алфавита (A-G). На рис.12. приведена конфигурация цифр 0…9, выраженная в семисегментном коде.

Рис.12.