Курсовая работа: Цифровой измеритель разности двух напряжений

signal GND: integer range - 10 to 10;

signal nznak,R1: std_logic;

signal K1,K2,NK1,NK2,NK1_takt,NK2_takt,clock: std_logic;

signal takt,zk1,zk2,zk1_k2,zk2_k1,Res: std_logic;

begin

u1: dif_oy port map (In1=>Ua, In2=>Ub,Out1=>Ua_b);

u2: comp port map (U1=>Ua_b, U2=>GND, U_out=>nznak);

u3: not_op port map (a=>nznak, z=>znak);

u4: GLIN port map (out1=>GLN,not_out1=>NGLN);

u5: comp port map (U1=>Ua_b, U2=>GLN, U_out=>K1);

u6: comp port map (U1=>Ua_b, U2=>NGLN, U_out=>K2);

u7: Or_op port map (a=>K1, b=>K1,c=>K1, z=>NK1);

u8: not_op port map (a=>K2, z=>NK2);

u9: gen port map (gen_out=>takt);

u10: And_op port map (a=>NK1,b=>takt,z=>NK1_takt);

u11: And_op port map (a=>NK2,b=>takt,z=>NK2_takt);

u12: Or_op port map (a=>NK1_takt,b=>NK2_takt,c=>NK2_takt,z=>clock);

u13: counter port map (reset=>Res,up=>clock,C_out=>cod_out);

u14: not_op port map (a=>NK1,z=>zk1);

u15: not_op port map (a=>NK2,z=>zk2);

u16: And_op port map (a=>zk1,b=>NK2,z=>zk1_k2);

u17: And_op port map (a=>NK1,b=>zk2,z=>zk2_k1);

u18: Or_op port map (a=>zk1_k2,b=>zk2_k1,c=>zk2_k1,z=>R1);

u19: And_op port map (a=>R1,b=>Reset1,z=>Res);

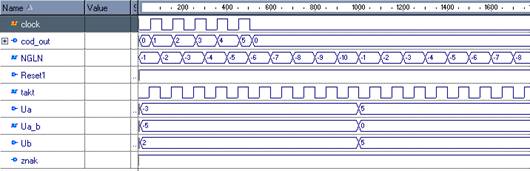

В результате анализа модели устройства получена следующая временная диаграмма.

Рисунок 3.5 - Временная диаграмма, полученная при анализе модели устройства

Из диаграммы видно, что на выходе cod_out формируется цифровой код, эквивалентный разности напряжений Ua-Ub, поданных на вход устройства. С выхода znak снимается знак разности: 1, если Ua-Ub<0 и 0 если Ua-Ub>=0.

4.1 Анализ пригодности разработанных моделей для имплементации в PLD

При проектировании цифрового устройства, для последующего имплементации в PLD, появляется ряд дополнительных трудностей, связанных с невозможностью использования некоторых типов данных и языковых конструкций. Так же приходится учитывать особенности имплементации для ПМЛ разных фирм и устанавливаемые ограничения: максимальная частота, количество доступных элементов и т.д. Наиболее эффективным способом в этом случае является построение структурных моделей с использованием библиотек компонентов поставляемых производителем конкретного типа ПМЛ. Однако в данной расчетно-графической работе этого не было сделано, так как основной целью было - приобретение навыков построение моделей отдельных узлов и структурных моделей. В целом при построении моделей цифровых узлов не использовались запрещенные языковые конструкции и типы данных, также были учтены ограничения на количество доступных элементов памяти и максимальную частоту сигнала.